Digital course

Want to learn how to design digital chips?

Learn to design your own ASIC and get it fabricated! Thanks to the open source Process Development Kit from Google and Skywater and the LibreLane ASIC flow, we now have the opportunity to get involved in this exciting field without signing NDAs or paying a fortune for tool licenses.

GCC revolutionised compiling, Linux revolutionised computing. Android revolutionised phones. Arduino revolutionised microcontrollers. RISCV is revolutionising ISAs. The next step is open source silicon.

This course will give you the experience of designing your own microchip using free and open source tools and getting it manufactured on an open source PDK.

Of the 650 people who have taken the course, 200 have submitted designs for MPW2, MPW3, MPW4, MPW5, MPW6, MPW7, MPW8 and Tiny Tapeout.

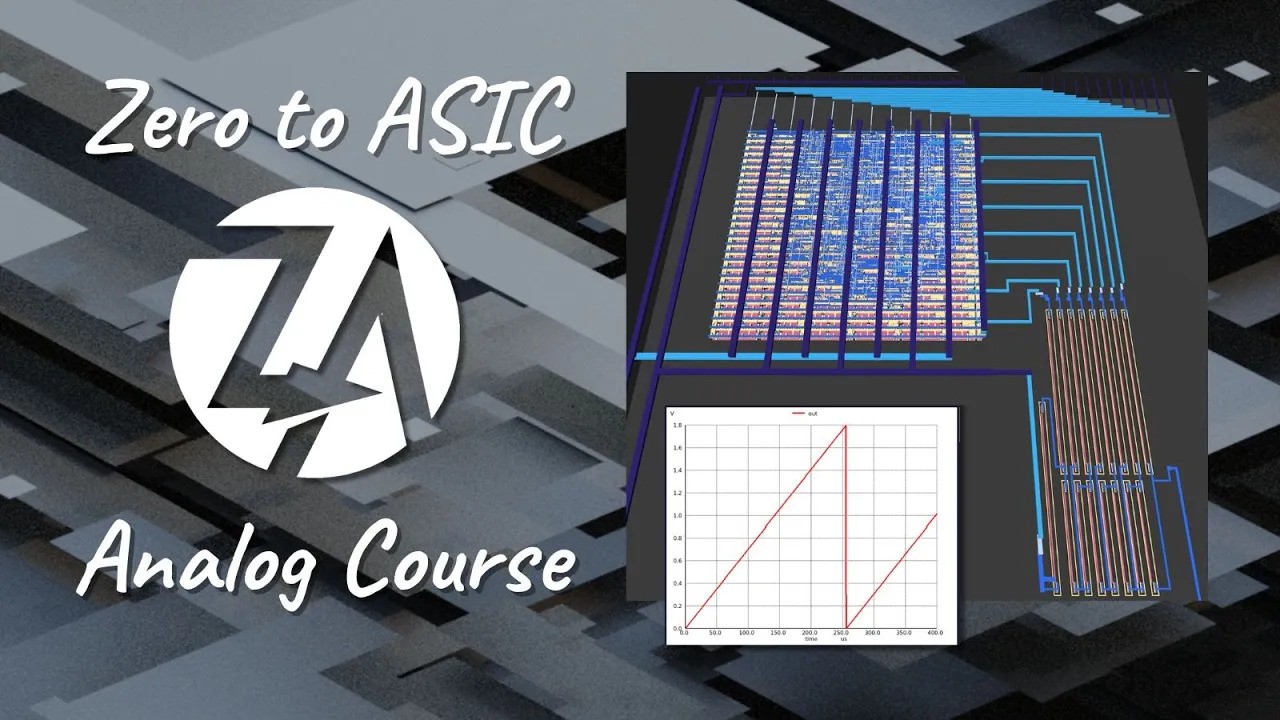

Analog course

Want to learn how to design analog chips?

The Zero to ASIC Analog course will guide you through the process of taping out analog integrated circuits using open-source tools. While digital design often relies on hardware description languages and automated synthesis, analog design involves more in depth simulation and drawing circuit layouts by hand. You’ll learn to use tools like Xschem for schematic capture, NGspice for simulation, and Magic for layout.

The course focuses on the Sky130 Process Design Kit, a readily available open-source PDK well-suited for mixed-signal designs. You’ll gain practical experience by drawing schematics, simulating, and ultimately taping out your own analog circuits, culminating in the fabrication of a physical chip through Tiny Tapeout.

Join the growing movement of open source analog chip designers by taking this course!

Testimonials

I didn't know what to expect regarding formal verification and that was delightful, I thought it was very fun and totally new to me.

Tommy Thorn (digital course)

Don't think twice about taking this course, It uses a unique method, you get to do stuff yourself and learn by playing around. Getting through this course and designing my own ASICs was the greatest experience of my life.

Seyed Farhad Modaresi (digital course)

What I learned in 6 weeks in this course would have taken me 6 months on my own. This is a great way to accelerate it.

Mike Thompson (digital course)

Learn more!

- Sign up to the Newsletter,

- Find out more about your instructor Matt Venn,

- Read an Article,

- Learn some Terminology.