Short articles about my experience with the Google/Efabless/Skywater130 ASIC process, interviews and any other related topics I think are interesting.

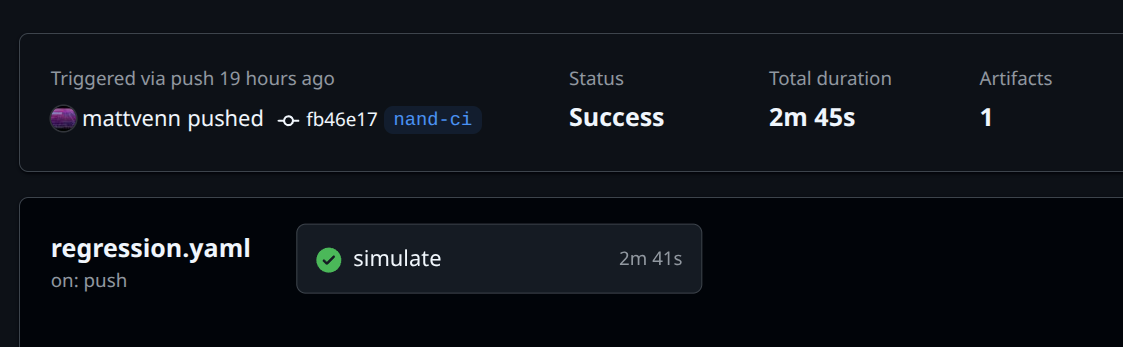

Testing projects with GitHub actions

For the past two years, I’ve used GitHub Actions to automatically test the install instructions for the Zero to ASIC course. Now, as I work on a major update, I’m taking it further: I’m adding CI tests for every one of the 10 practical projects.

The goal? Make sure students never run into out-of-date instructions or broken software.

To do this, I’ve been exploring Harald’s IIC-OSIC-TOOLs Docker image and built a new composite GitHub Action.

Sky130 Inverter Instructions

Review of 2024 and aims for 2025

Wow what a year! In this post I’m going to look back over 2024 and share some of my highlights and the goals I met and failed. Then I’ll share my ambitions and predictions for 2025.

With all the open source tapeouts, events, workshops and news, there’s a ton to cover - so let’s jump in!

I aimed for 2000 new people to get started with open source silicon via my courses and tiny tapeout.

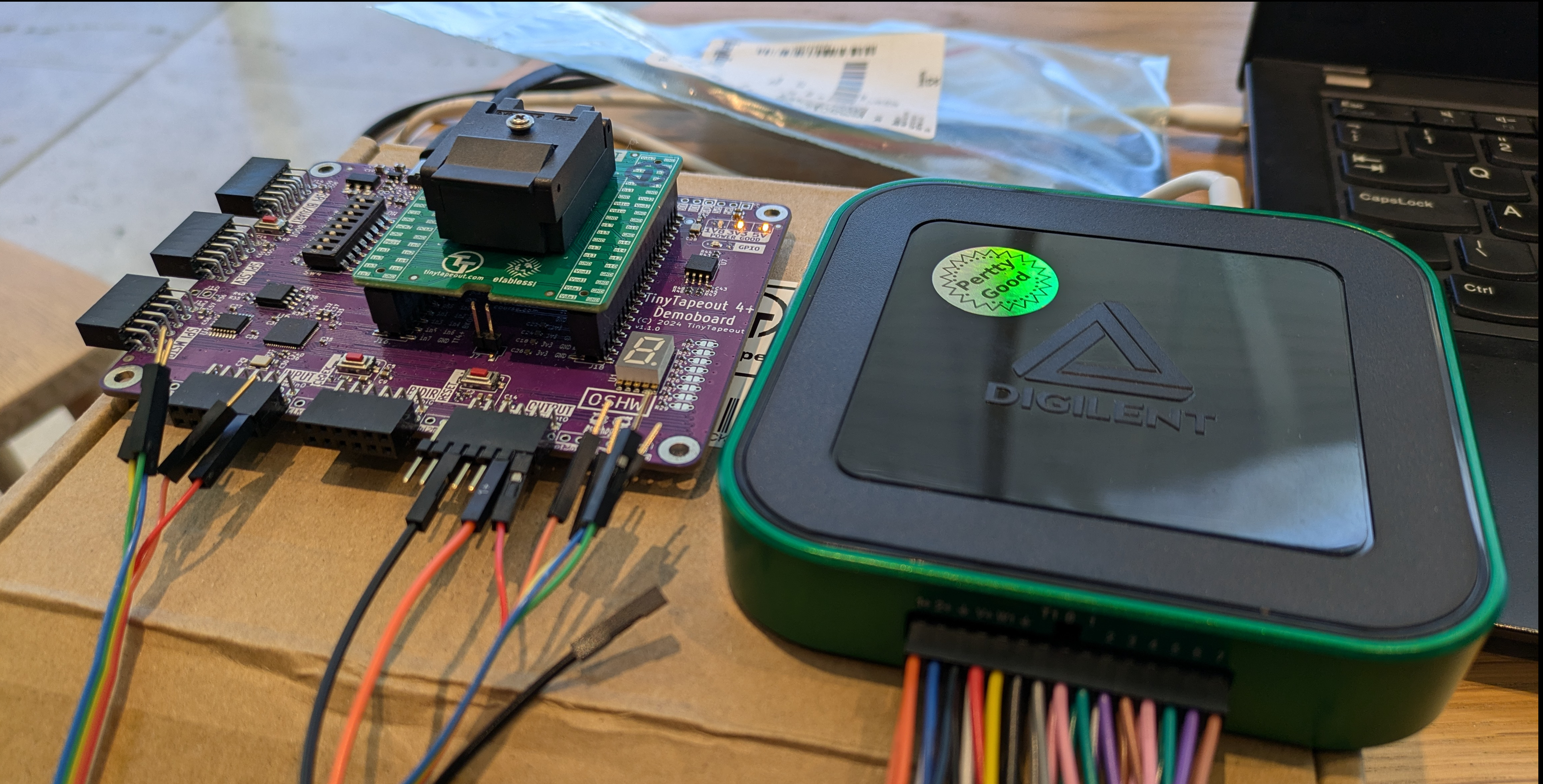

Test Equipment Grant

Applications for the grant is now closed.

It’s become a cliche, but hardware is hard! One reason why hardware is harder than software is that the time between revisions is often longer. We need to wait for new PCBs, or for components to be delivered. Or for more new PCBs after we realise we got it wrong!

Another reason is that it can be expensive, and not just for the physical components. We generally need more of a lab than software developers. Not just soldering irons and good lighting. Test gear is essential for learning how your circuit is actually behaving, matching simulation to the real world. And it’s usually expensive.

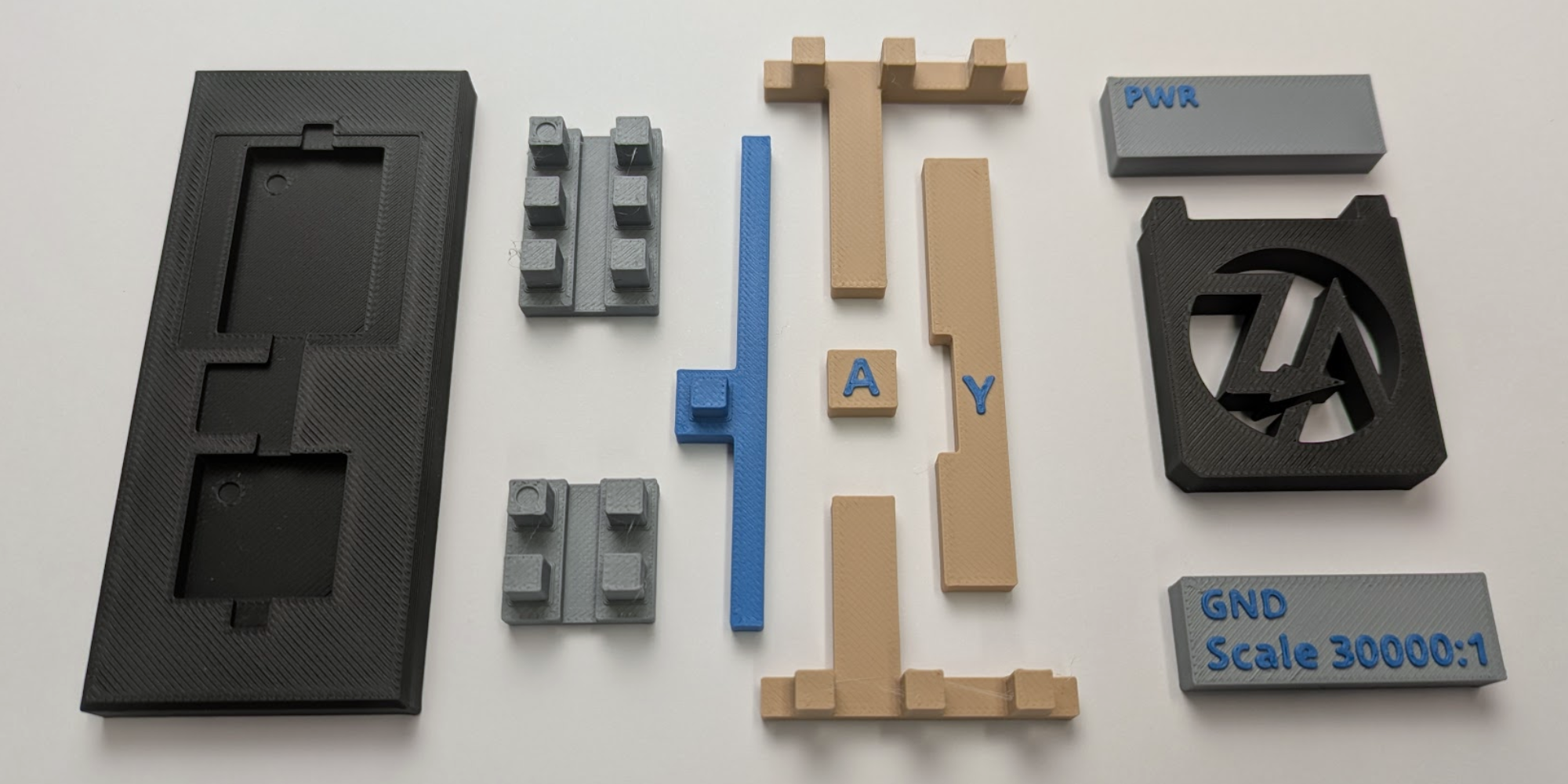

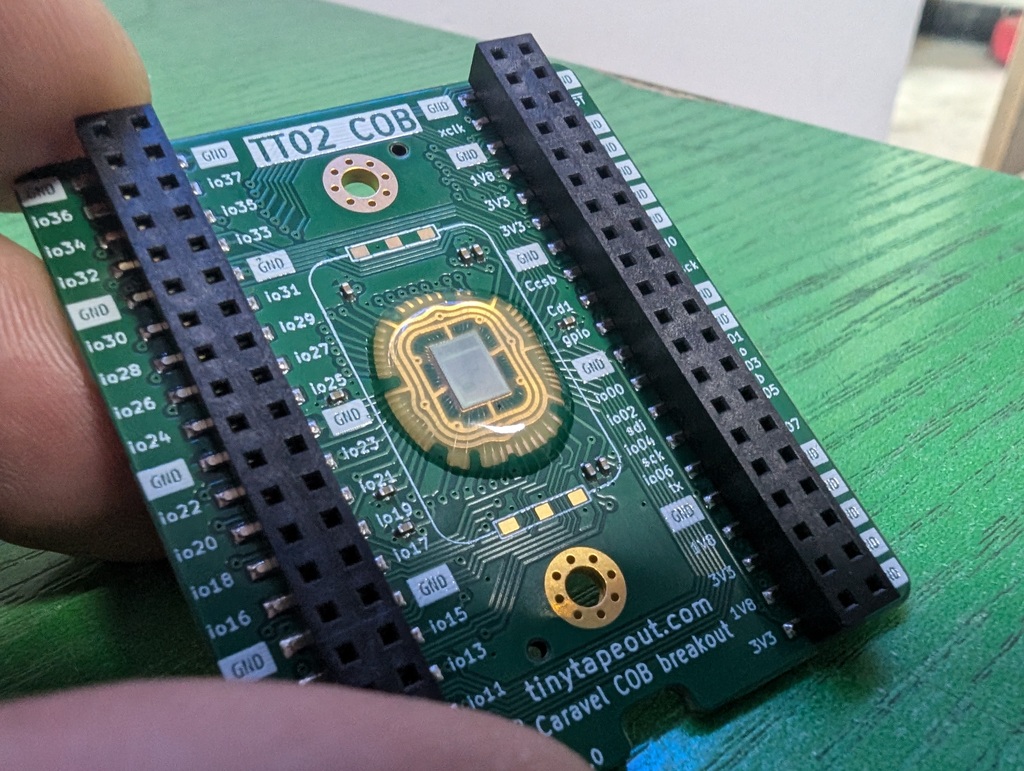

Chip On Board

Our first COB (chip on board) chips are working! This has been a dream of mine for a few years, and it’s finally a reality!

We’re used to seeing chips as little black boxes on a circuit board, but what’s inside?

The first part of the journey started with Tamas creating this cool circuit board.

Tiny Tapeout 9

Tiny Tapeout 9 closed with 95% utilisation! It was our best ever run, with 369 designs submitted from 21 countries.

Among the digital projects we had an Atari 2600 (with games), a wide range of CPUs and even some SDR projects.

On the analog side we had PLLs, opamps, ADCs, DACs and time to digital converters.

For all the projects, check the chip’s page.

I printed the datasheet, and it’s hefty! Download it here.

Get started with open source ASICs

In my recent video Getting started with open source ASICs, I provided an overview of the open-source silicon movement, highlighting key resources and tools while showcasing some inspiring projects.

The video starts by looking back at the game-changing moment in 2020 when Google, Tim Ansell, and Efabless announced their free shuttle program, making it possible for anyone to get their open-source chip designs manufactured. This sparked a wave of innovation, with many taking their first steps in ASIC design using open-source tools like OpenLane and the Skywater 130nm PDK.

My analog microelectronics journey

This article will give you some insight into my journey into the world of analog microelectronics, as told in my recent talk at ORConf 2024.

Back in 2020, inspired by Tim Ansell’s announcement of free tapeouts, I jumped headfirst into the world of open-source ASIC design. My first chip was a digitally focused project, reflecting my background in FPGA programming. It was amazing to see the power of digital abstraction—designing with ones and zeros, instantiating tons of transistors with a single line of code—but it also made me appreciate the incredible complexity hidden beneath the surface.

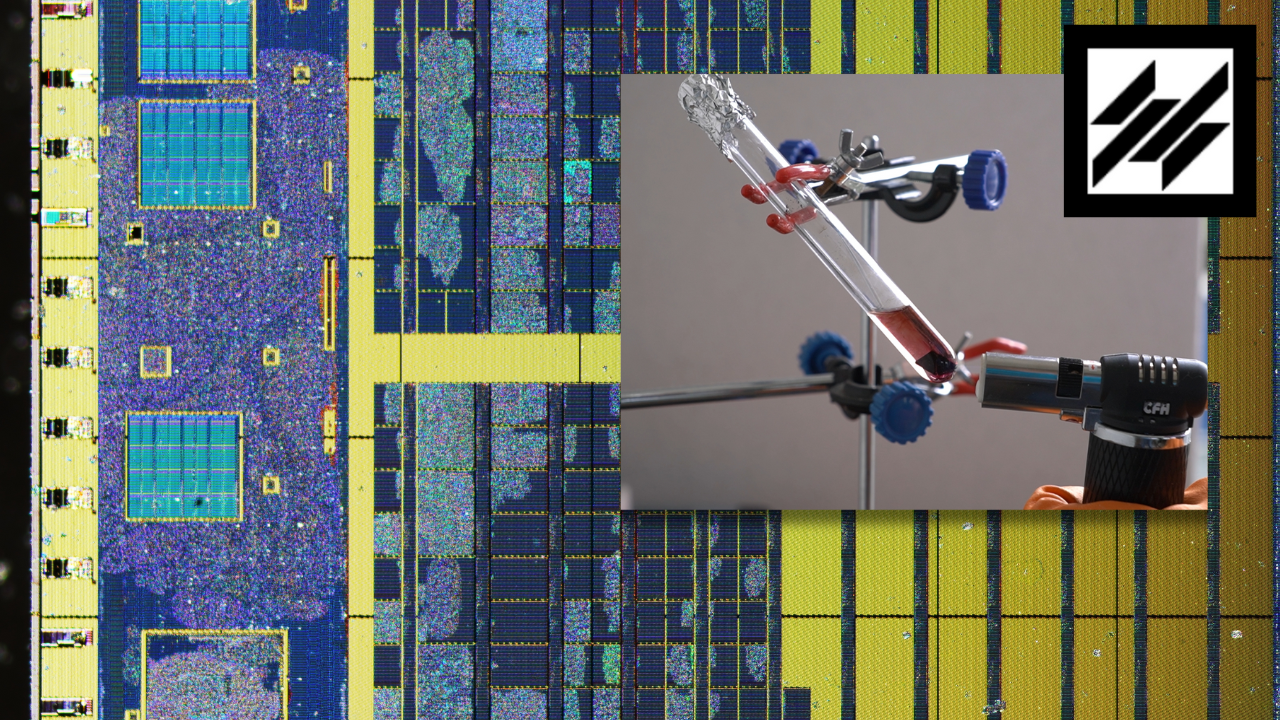

Looking inside an open source ASIC with Zeptobars

In this interview, I met up with Michael from Zeptobars in Zurich, Switzerland, where we use acid to decapsulate one of my Tiny Tapeout chips. This technique involves using acid to remove the protective epoxy layer of a chip, revealing the silicon die underneath. Decapping is commonly used to analyse the construction of integrated circuits. Michael usually decapsulates chips designed by others, sometimes decades ago, but this time one of the designs is his own.

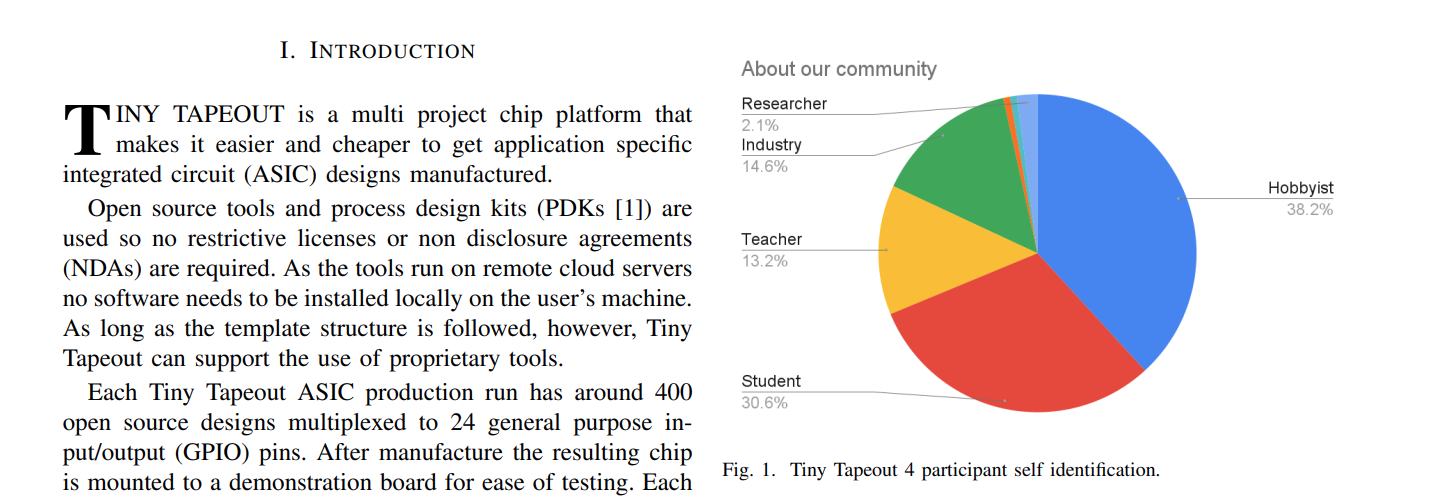

Tiny Tapeout IEEE paper

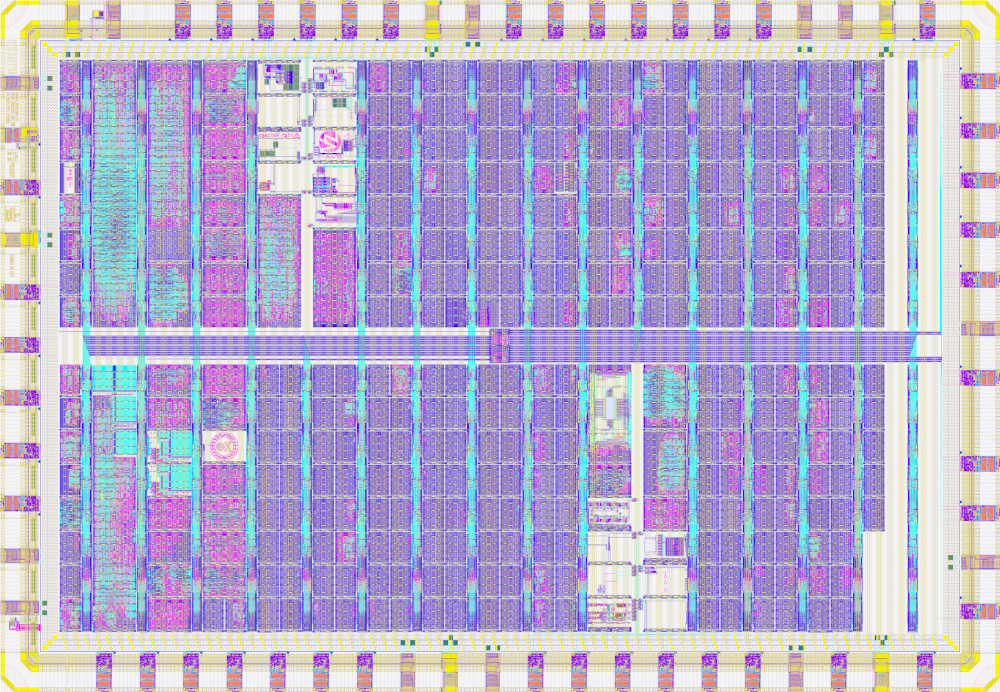

I’m very happy to announce that my paper about Tiny Tapeout has just been published by the IEEE solid state circuits magazine!

Tiny Tapeout aims to make it easier and cheaper than ever to design and manufacture custom Application-Specific Integrated Circuits (ASICs). I originally conceived of the idea in September 2022 as a way to guarantee silicon for my course participants.

If you’re an IEEE member, you can read it here: https://ieeexplore.ieee.org/document/10584359, otherwise you can read the preprint: https://www.techrxiv.org/users/799365/articles/1165896-tiny-tapeout-a-shared-silicon-tapeout-platform-accessible-to-everyone