Short articles about my experience with the Google/Efabless/Skywater130 ASIC process, interviews and any other related topics I think are interesting.

The MOnSter 6502 - a 6502 processor out of discrete transistors

I had the chance to interview Eric Schlaepfer about his MOnSter 6502, a 6502 processor made out of discrete transistors. For me, one of the most interesting things about this project are the similarities to ASIC design, for example Eric wrote his own LVS tool.

You can find out lots more at his website.

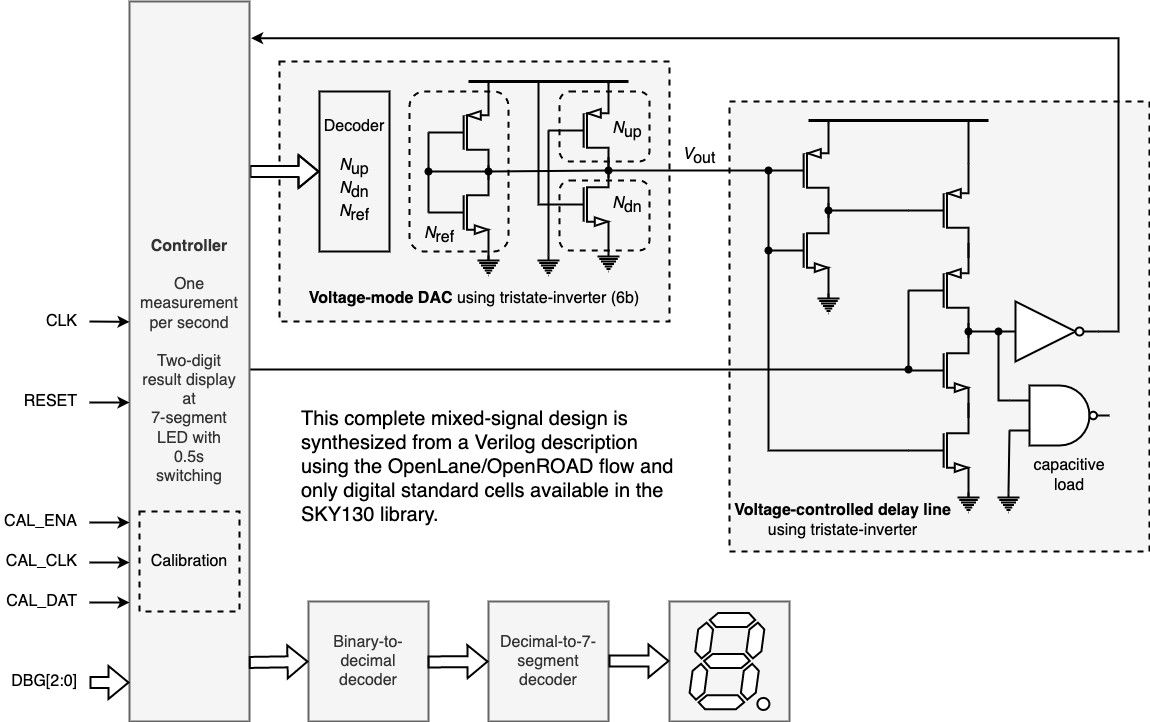

Analog with Digital Standard Cells

Harald Pretl made a fascinating submission to Tiny Tapeout 3, an analog circuit made from digital standard cells.

It builds a DAC out of a lot of tristate inverters, and a big capacitor by ganging up a lot of NAND gates.

In this interview with Harald we discuss how it works and how he made it and simulated it.

You can check his design here, including the source and GDS.

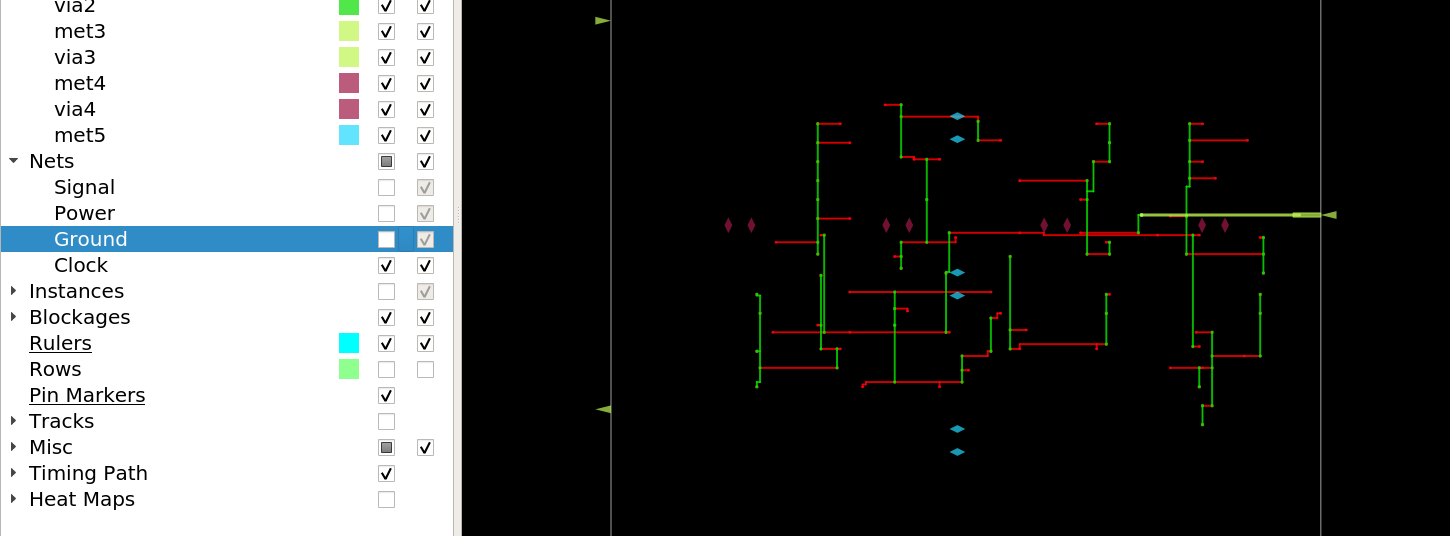

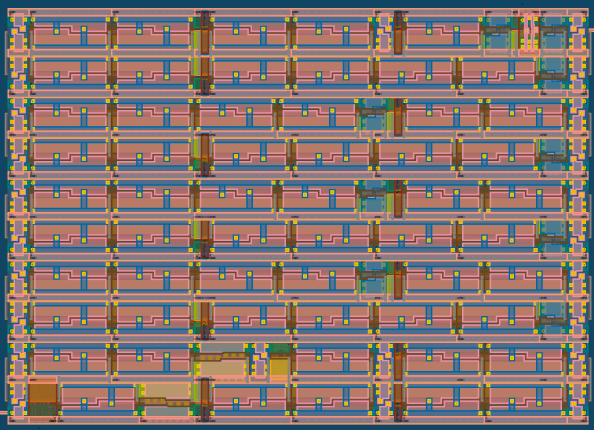

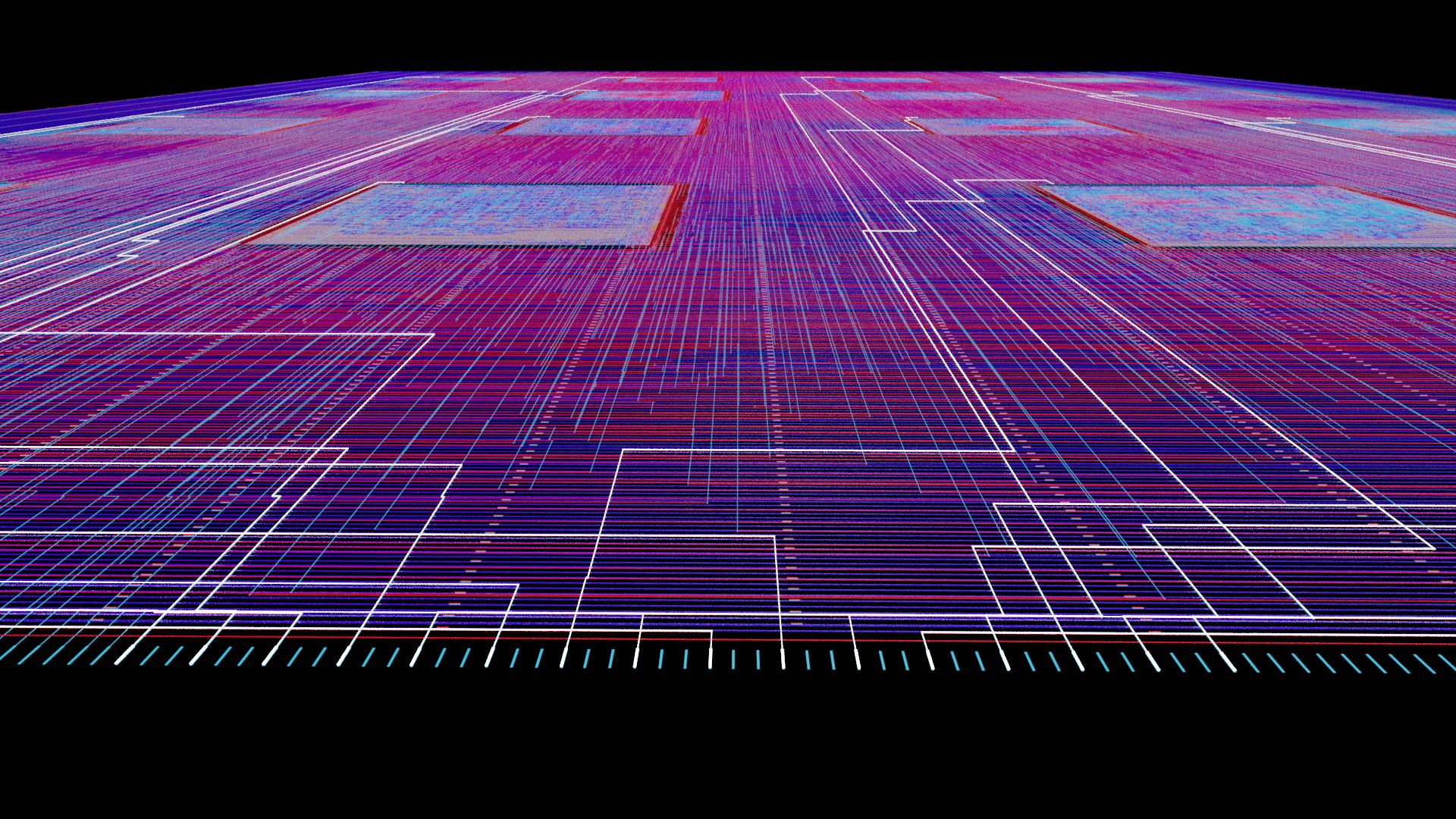

OpenROAD GUI

The OpenROAD GUI is a great way to explore your ASIC design. You can:

- View various types of heatmaps, including

- Placement density

- Power density

- Routing congestion

- IR drop

- Trace nets,

- View the clock tree,

- Inspect timing and more.

I recently spoke with Matt Liberty, and OpenROAD maintainer, and he showed me how to inspect a simple design.

OpenLane

If you’re using OpenLane to harden your ASIC designs, and you want to use the GUI, you might hit a segfault. If so, you’ll need to modify the OpenLane top level Makefile.

Review of 2022 and aims for 2023

Welcome to my highlights from 2022! It was a big year for open-source silicon, especially the Zero to ASIC course and Tiny Tapeout. Let’s look at some of the highlights and then some aims for 2023.

Here are a few of the highlights:

- Four Zero to ASIC course tapeouts: MPW5, MPW6, MPW7, and MPW8

- Rolled out Tiny Tapeout 1 and 2, helping nearly 250 people tapeout their designs,

- I personally submitted my 19th tapeout

- Presented and hosted a Tiny Tapeout workshop at the Hackaday SuperCon in Novemeber 2022. Met tons of people, including Sam Zeloof @szeloof.

- YouTube Channel had 82k views and 2.5k new subscribers

- Introduced Siliwiz

Zero to ASIC course Tapeouts

The Zero to ASIC course continued to grow, we now have 280 students and made submissions to four multi-project wafers (MPW).

Cloud Tools for ASIC Development

ASIC development tools have often been inaccessible due to cost and complexity. Even as free, open-source tools have become available, the complexity of building and installing the tools has slowed their use by would-be designers.

A challenge in making ASIC development more accessible has been to provide free, easy-to-use development tools. Thankfully development of cloud-based tools using open-source software are making chip design easier than ever.

In June 2022, I had the chance to talk with @Proppy, a Tokyo-based Google engineer who’s enabling people to collaborative ASIC in the cloud with Jupyter and Colab notebooks.

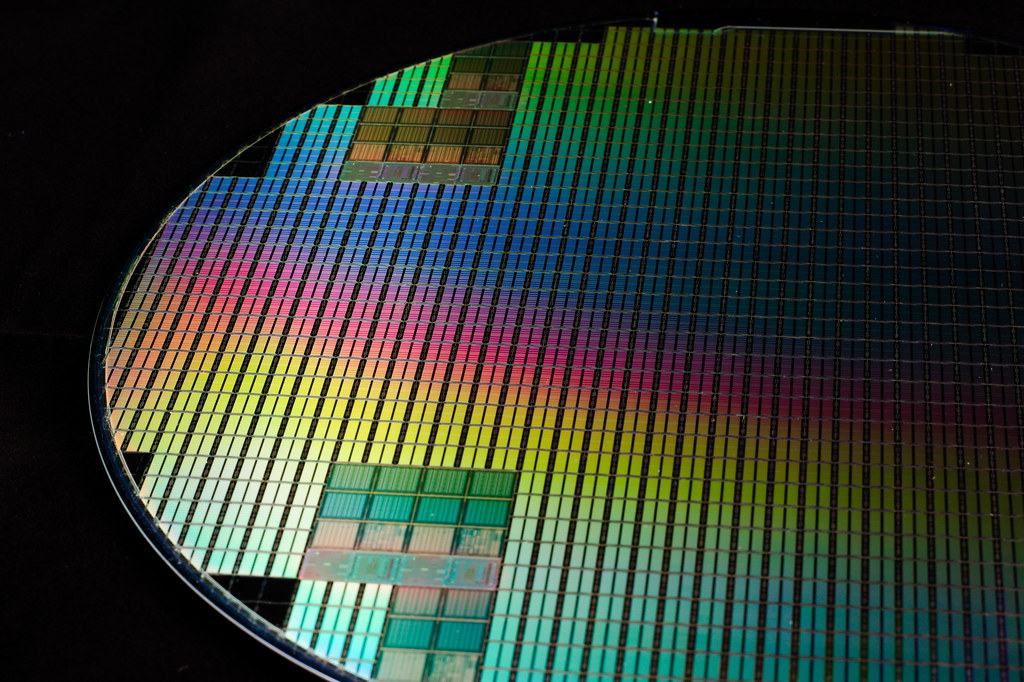

GlobalFoundries 180nm Fab

An exciting new opportunity for developing open-source silicon reached fruition at the end of 2022!

GlobalFoundries (GF) teamed up with Google to fund open-source projects using GF’s foundry and their open-source 180nm PDK GF180.

Open-source PDKs like GF180 and Skywater 130nm are essential for making silicon design more accessible. To now have GlobalFoundries involved with fabricating designs will hopefully mean increased opportunities to turn designs into silicon.

GF180’s first multi-project wafer (MPW) tapeout was in December 2022, and several people from the Zero to ASIC and Tiny Tapeout communities were able to submit designs. Here are some highlights:

Submit Tiny Tapeout Projects to an MPW

Using the Tiny User Project tool, people can quickly submit a Tiny Tapeout design to the MPW lottery. The low barrier to entry makes this a great tool to try variations on a design, test faster I/O speeds on an MPW tapeout, or simply compare tapeout processes using a different submission venue.

@Proppy developed the an easy-to-use tool as an extension to the Tiny Tapeout flow.

Proppy’s template repository uses GitHub actions to add a design to the Efabless Caravel User Project. The actions automatically perform the steps requried to harden the design, generate the necessary GDS files, and even generate a convenient GDS viewer. Additionally, the actions output useful reports on cell resource utilization, manufacturability errors, and the precheck results.

Tiny Tapeout 2 submitted for manufacture

I’m happy to announce that Tiny Tapeout 2 was successfully submitted for manufacture in December 2022! 164 designs were included on the tapeout.

Update! Tiny Tapeout 2 chips are back and working!

If you’re unfamiliar, Tiny Tapeout is an educational project that makes it easier and cheaper than ever to get your digital designs manufactured on a real chip! We had a first trial, Tiny Tapeout in September 2022 that was destined for MPW7.

Zero to ASIC course Ticket Grant

I am excited to introduce a grant for the Zero to ASIC course.

The grant will provide a Silicon-level ticket for selected participants. Two grants will be awarded per month.

Course goals

This course aims to revolutionize open-source silicon by training engineers, hobbyists and enthusiasts to make their own ASICs. During the course, you will design a circuit that will be submitted to the Google lottery MPW to be manufactured in silicon!

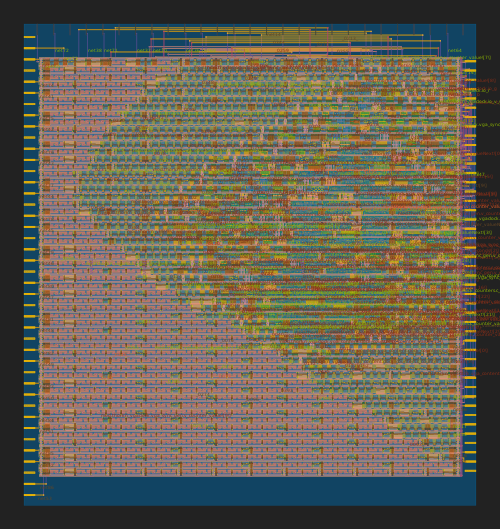

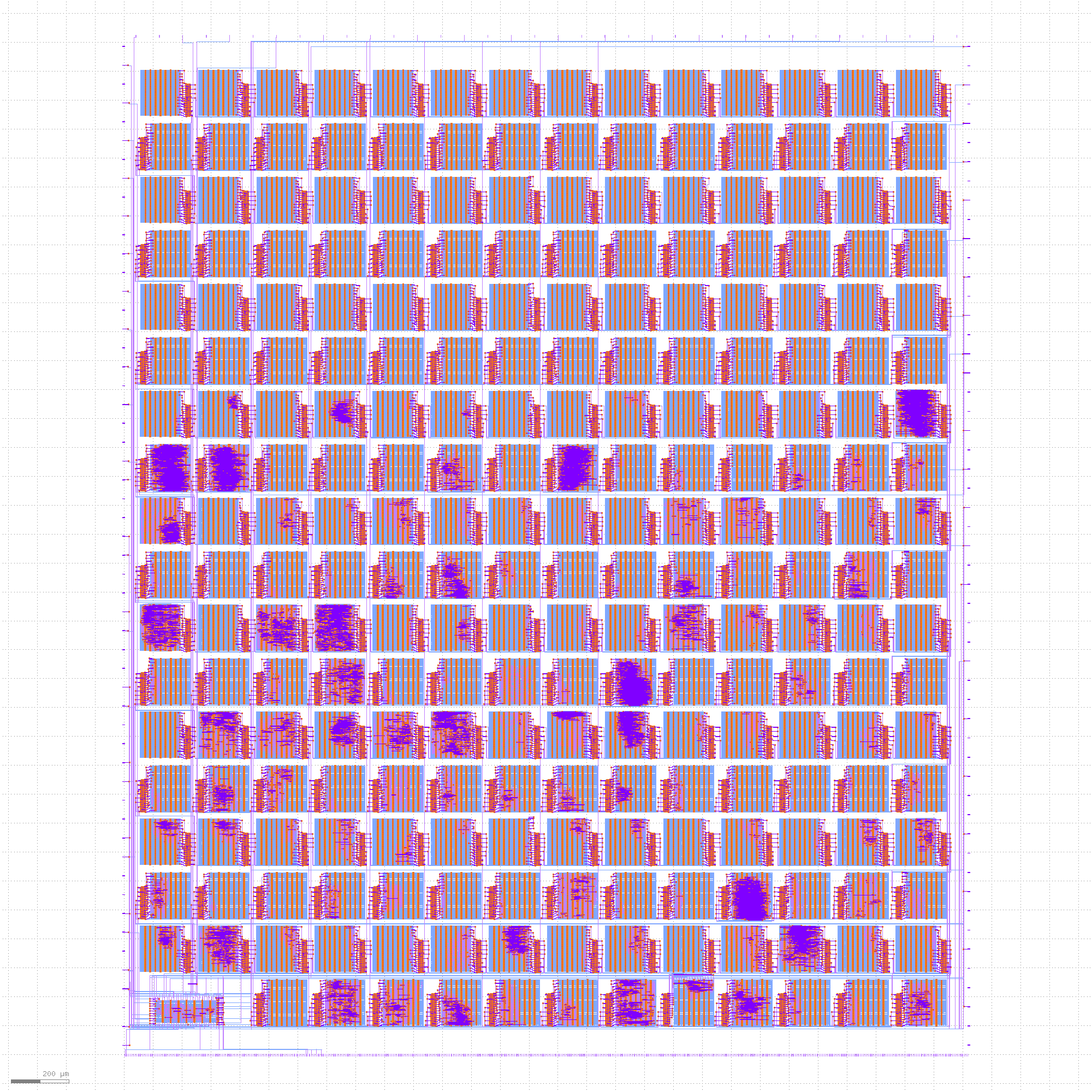

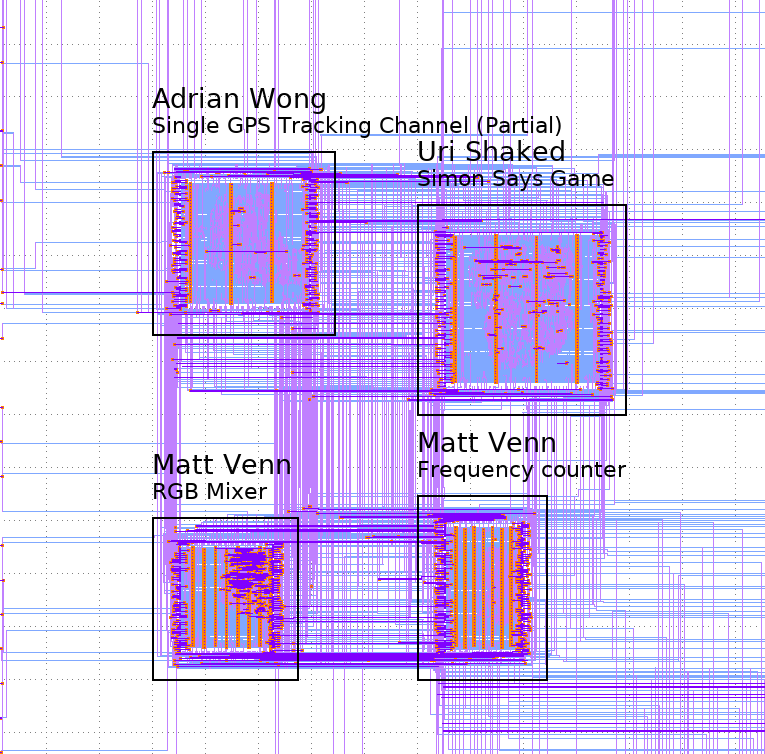

MPW8 submitted!

We submitted for MPW8! Special congratulations to Adrian Wong for the course submission!

We still managed to get 4 projects in the submission…not bad for a deadline of New Year’s Eve.

The projects include a partial implementation of an L1 GPS tracking channel by Adrian Wong, a Simon Says game implementated by Uri Shaked, and 2 demo submissions (frequency counter and RGB mixer) from me.

Here’s the github repo for the group submission and the Efabless project.