LibreLane

LibreLane is an Open Source ASIC tool. You can download it from here.

LibreLane is the new name for OpenLane. After Efabless shutdown the project was transferred to the FOSSi Foundation.

OpenLane was released in 2021 and you can watch Mohamed Shalan’s OpenLane FOSSI dialup presentation to find out more about it.

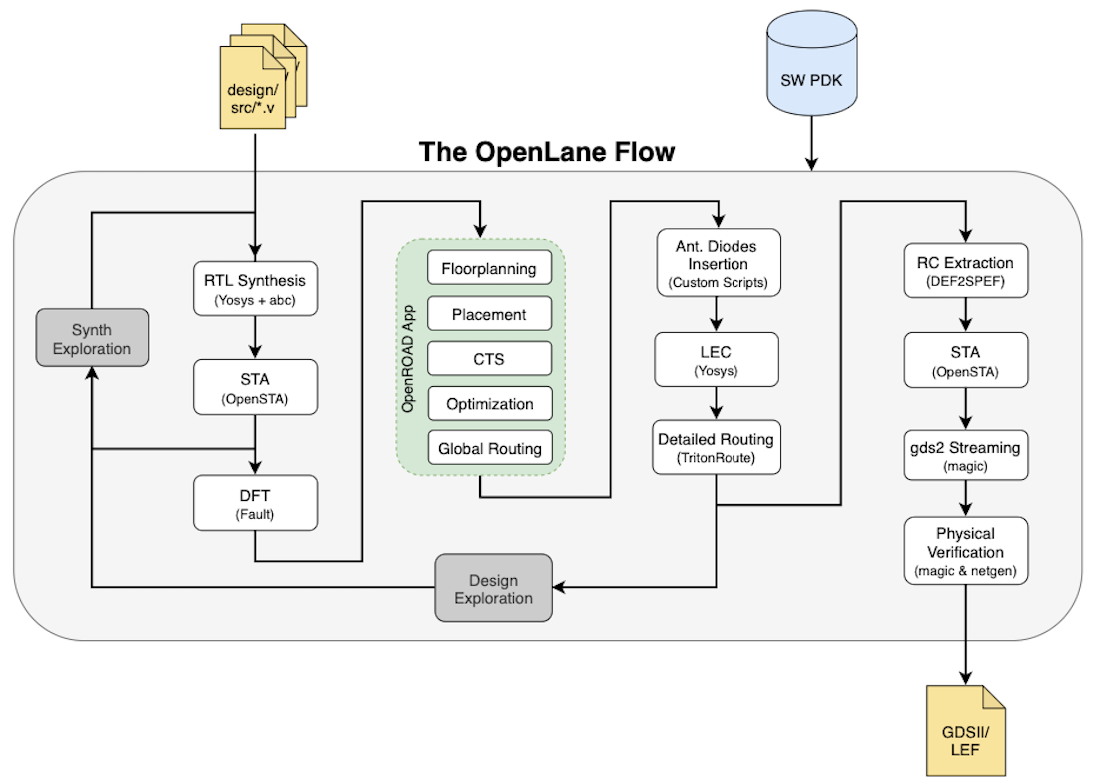

Here’s the overview:

We put our HDL in at one end, and out the other comes the GDS2 files that are the standard file format for the foundry.

The most fundamental steps are:

- Synthesis

- Floor planning

- Place and Route

- sign off: Layout vs Schematic, Design Rule Check, Static Timing Analysis

To see more about LibreLane’s output files - check this article

OpenROAD

LibreLane is an open source ASIC flow built using OpenROAD. OpenROAD is a project funded by DARPA to develop open source ASIC tooling.

Here is the OpenROAD documentation and Tutorials and some useful resources.

You can watch some interviews I did with Tom Spyrou, lead dev of OpenROAD here:

Tom also did a presentation for OpenTapeOut.

Course feedback

I found that during the week that I was getting prepared for MPW4 was probably the happiest I've been in a long time. I like the challenge and difficulty of it, but it's still done in an approachable way that was not completely over my head.

Dylan Wadler (digital course)