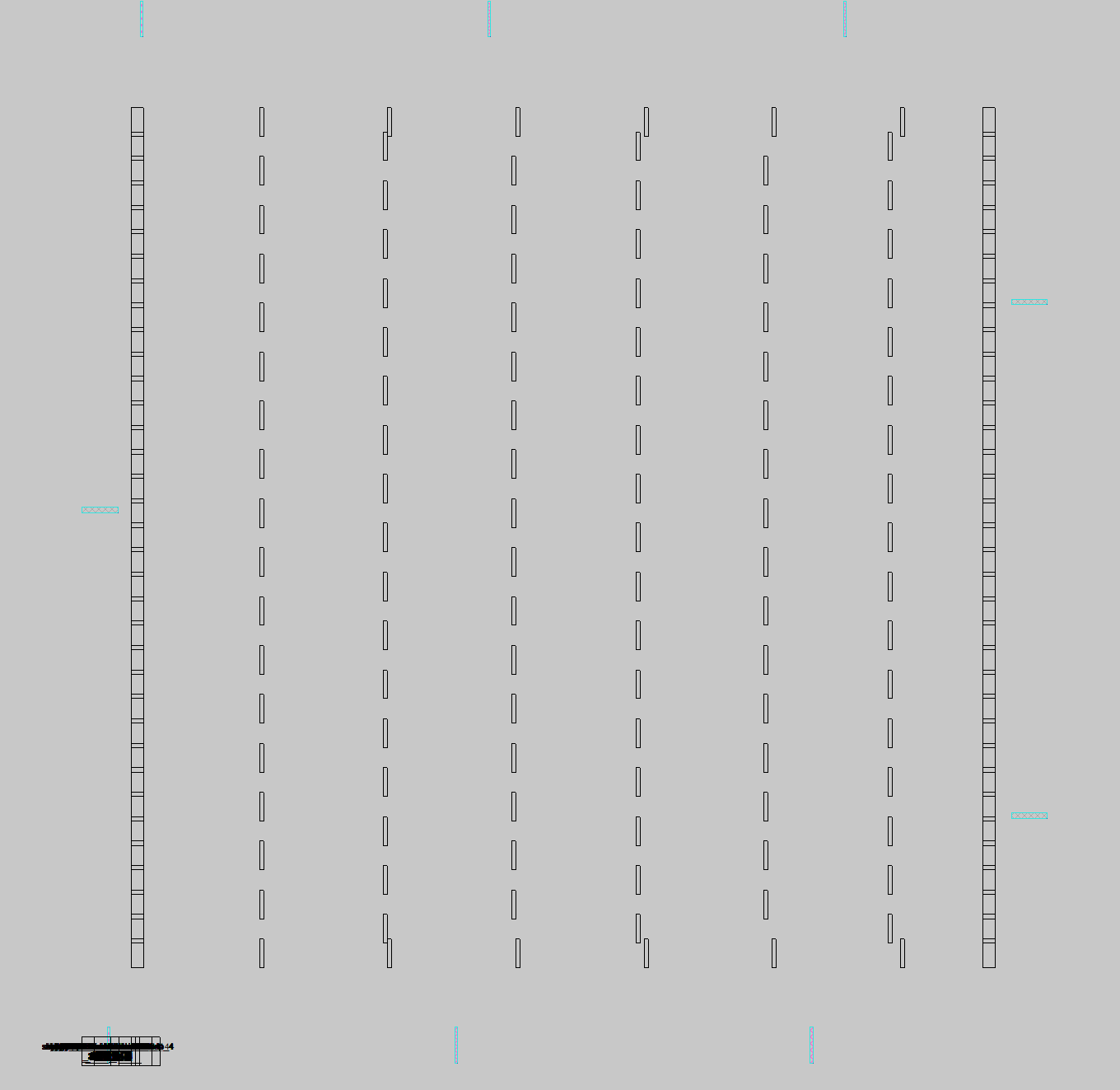

Floorplan

The floorplanning stage is where LibreLane decides how big an area we need to fit everything in. All the required standard cells are placed in the bottom left corner, ready for the place and route stage.

All the little rectangles in the centre are called tap cells. They make sure the MOSFETs work correctly by connecting the P doped substrate to ground and the N-wells (that insulate the P-type MOSFETS) to power.

The slightly bigger rectangles at the edges are decoupling capacitors. After the routing is finished, any spare space is filled up with decoupling capacitors. The job of these capacitors is to make sure that all the cells get a nice smooth power supply.

Course feedback

The Zero to ASIC course was great! Through this course I became more proficient with Verilog and started to not just appreciate, but actually enjoy the design verification! It offers the glimpse at the superpower too - seeing the traces of the original design in what used to be just squiggly lines of the masks before. Plus, I am getting my own piece of a silicon 🙂

Renaldas Zioma (digital course)