Below you will find pages that utilize the taxonomy term “ASIC”

Review of 2024 and aims for 2025

Wow what a year! In this post I’m going to look back over 2024 and share some of my highlights and the goals I met and failed. Then I’ll share my ambitions and predictions for 2025.

With all the open source tapeouts, events, workshops and news, there’s a ton to cover - so let’s jump in!

I aimed for 2000 new people to get started with open source silicon via my courses and tiny tapeout.

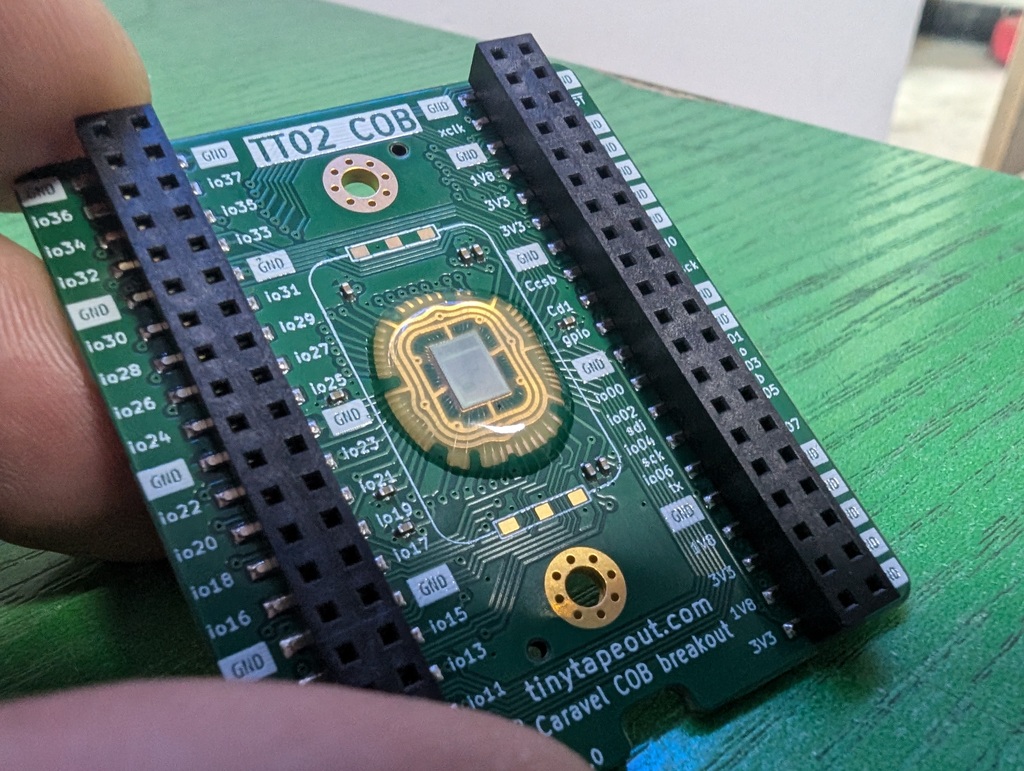

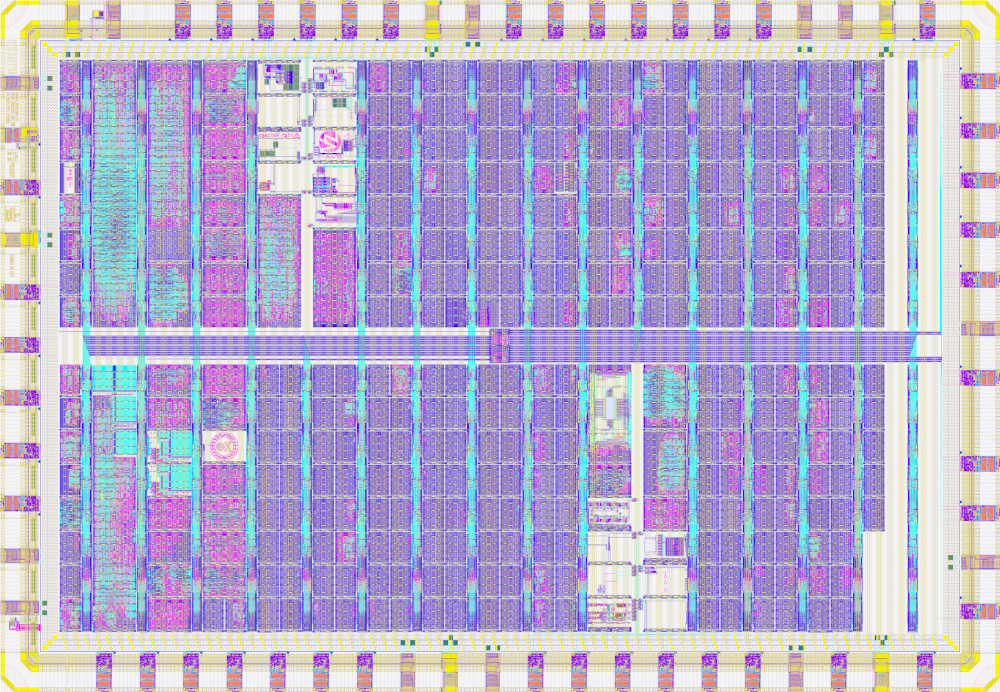

Chip On Board

Our first COB (chip on board) chips are working! This has been a dream of mine for a few years, and it’s finally a reality!

We’re used to seeing chips as little black boxes on a circuit board, but what’s inside?

The first part of the journey started with Tamas creating this cool circuit board.

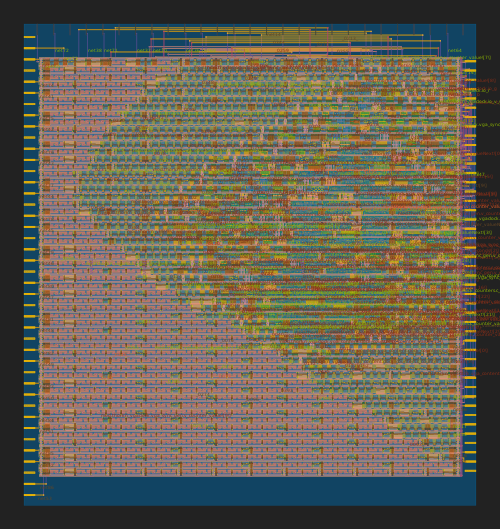

Tiny Tapeout 9

Tiny Tapeout 9 closed with 95% utilisation! It was our best ever run, with 369 designs submitted from 21 countries.

Among the digital projects we had an Atari 2600 (with games), a wide range of CPUs and even some SDR projects.

On the analog side we had PLLs, opamps, ADCs, DACs and time to digital converters.

For all the projects, check the chip’s page.

I printed the datasheet, and it’s hefty! Download it here.

Review of 2023 and aims for 2024

Hi and happy new year! Welcome to my year in review post of 2023. We’ll revisit the biggest moments of open source semiconductors, the goals I failed and those I met, and set some new ones for 2024!

So, let’s start with the biggest news of 2023.

Last year saw the end of the Google sponsored lottery shuttles. We were expecting around another 8 shuttles for sky130, GF180 and the start of sky90. The last shuttle was GFMPW1, which closed late last year and the Sky 130 PDK is now in the safe hands of the chips alliance.

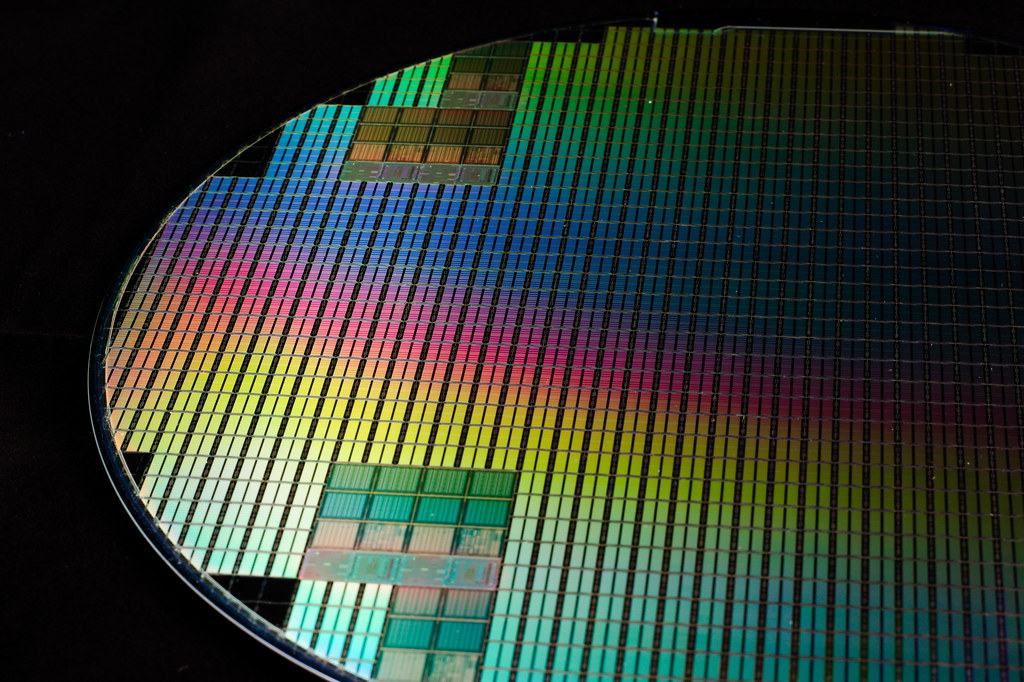

ASIC Necklace

For the last few years I’ve worn an old 4 inch wafer to conferences or whenever I’m teaching in person. People rarely get to handle a wafer and are always interested to know more.

While it’s a fantastic conversation starter, the problem with this necklace is that it’s too hip-hop, and not enough “15 million dollar Nikon Lithography Stepper”. To resolve this annoyance, I decided to make the most ridiculous ASIC bling possible - using my own chips of course! The only thing I kept from the old design was the quick release wafer.

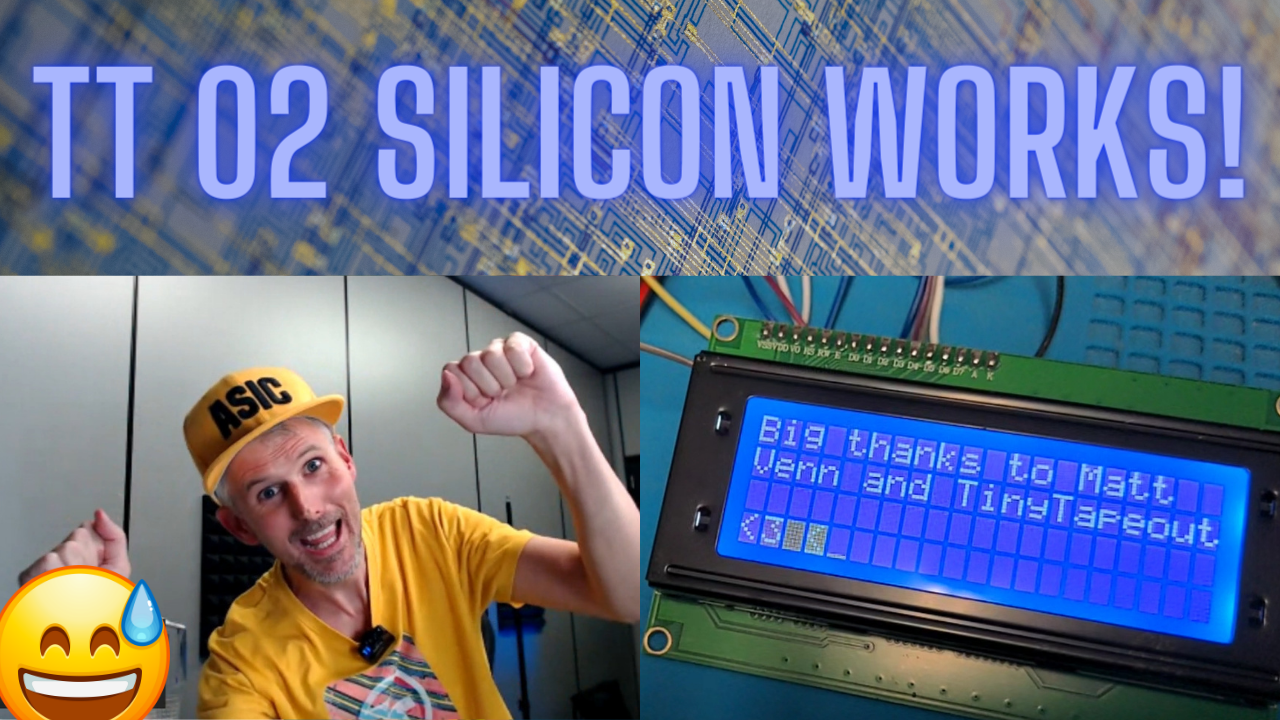

Tiny Tapeout 2 Silicon Is Alive!

We submitted Tiny Tapeout 2 back in December, and last week I received the chips from Efabless.

Most first chip designs fail, but you never hear about it because the big companies keep it a secret. So we thought - why not do the world’s first public silicon bring up?

Thankfully the chips worked, and you can watch the whole stream here.

We’ve since found 1 errata, but luckily not a show stopper.

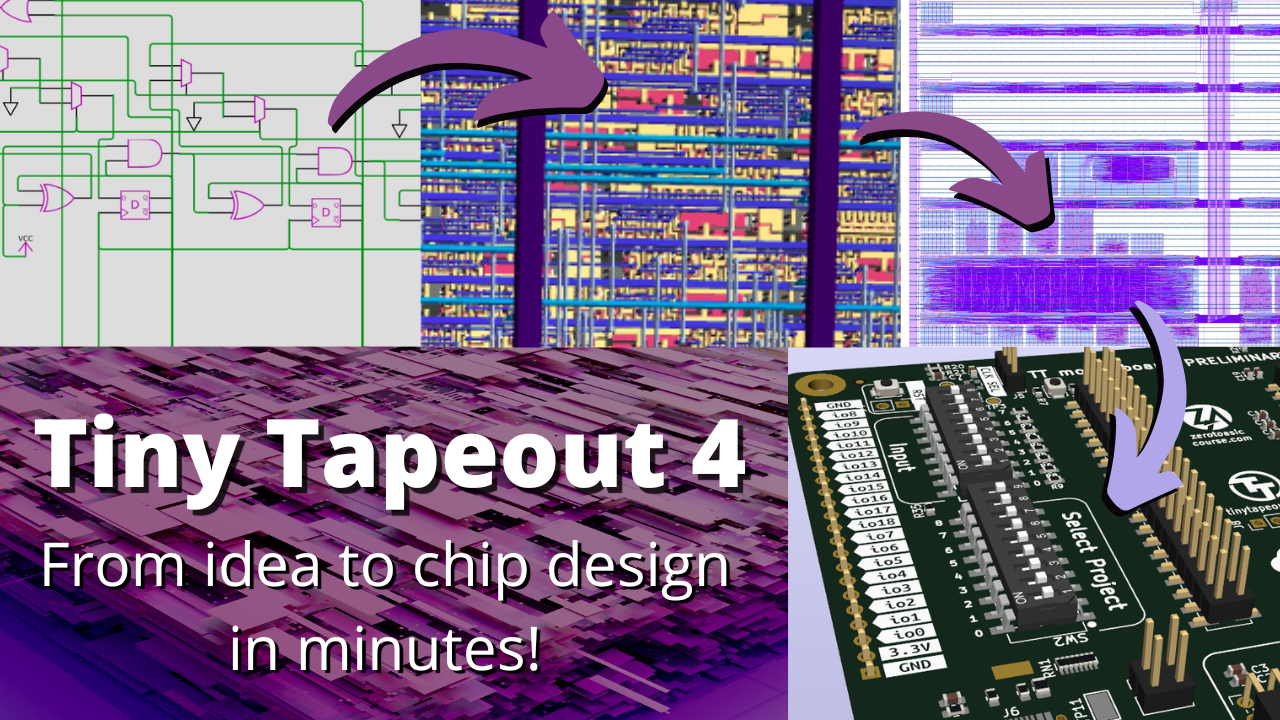

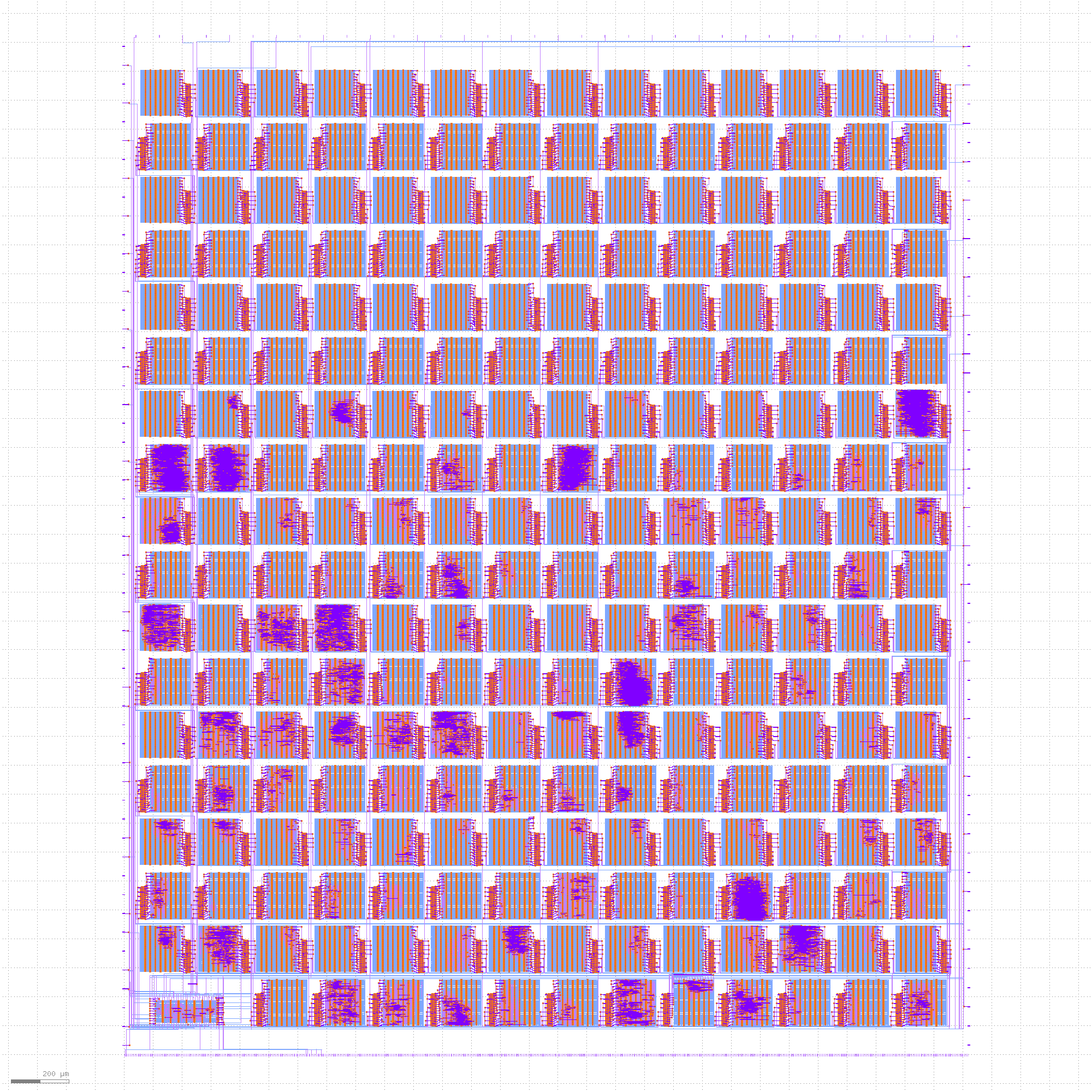

Tiny Tapeout 4

I’m very happy to have over 140 designs from 30 countries submitted to Tiny Tapeout 4!

Top level statistics:

- Total standard cells 82126

- Maximum cells used was 6813 for project 033

- Maximum utilisation was 87.18% for project 016

- Total wire length was 2607 mm

Thanks to everyone who submitted and all the contributors. Also a huge thanks to Efabless Corporation for sponsoring the project!

Tiny Tapeout 5 is already open and will close in early November 2023.

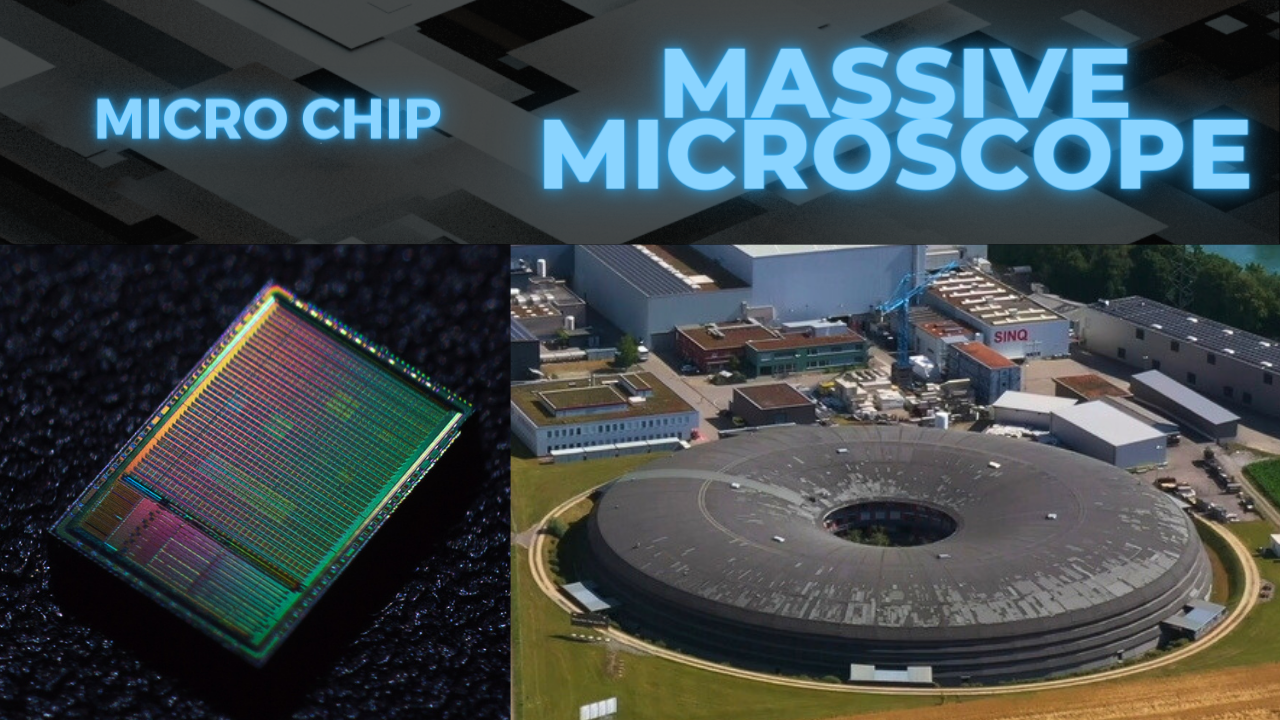

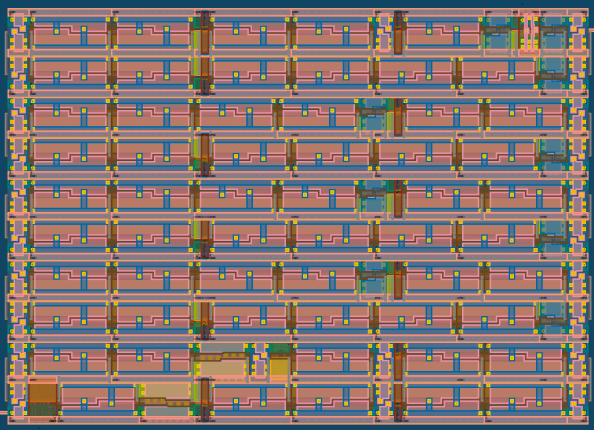

Looking inside my first ASIC with a particle accelerator

I got a once in a lifetime chance to use a particle accelerator to look inside my first ASIC!

It was amazing to be able to see all the different layers and match them up with the design files I sent to Efabless.

So join me on my journey to the Swiss Light Source at the Paul Scherrer Institut where I learnt how they use their synchrotron to make some awesome images!

I also have a public photo album if you want some SLS themed wallpaper!

Review of 2022 and aims for 2023

Welcome to my highlights from 2022! It was a big year for open-source silicon, especially the Zero to ASIC course and Tiny Tapeout. Let’s look at some of the highlights and then some aims for 2023.

Here are a few of the highlights:

- Four Zero to ASIC course tapeouts: MPW5, MPW6, MPW7, and MPW8

- Rolled out Tiny Tapeout 1 and 2, helping nearly 250 people tapeout their designs,

- I personally submitted my 19th tapeout

- Presented and hosted a Tiny Tapeout workshop at the Hackaday SuperCon in Novemeber 2022. Met tons of people, including Sam Zeloof @szeloof.

- YouTube Channel had 82k views and 2.5k new subscribers

- Introduced Siliwiz

Zero to ASIC course Tapeouts

The Zero to ASIC course continued to grow, we now have 280 students and made submissions to four multi-project wafers (MPW).

Cloud Tools for ASIC Development

ASIC development tools have often been inaccessible due to cost and complexity. Even as free, open-source tools have become available, the complexity of building and installing the tools has slowed their use by would-be designers.

A challenge in making ASIC development more accessible has been to provide free, easy-to-use development tools. Thankfully development of cloud-based tools using open-source software are making chip design easier than ever.

In June 2022, I had the chance to talk with @Proppy, a Tokyo-based Google engineer who’s enabling people to collaborative ASIC in the cloud with Jupyter and Colab notebooks.

GlobalFoundries 180nm Fab

An exciting new opportunity for developing open-source silicon reached fruition at the end of 2022!

GlobalFoundries (GF) teamed up with Google to fund open-source projects using GF’s foundry and their open-source 180nm PDK GF180.

Open-source PDKs like GF180 and Skywater 130nm are essential for making silicon design more accessible. To now have GlobalFoundries involved with fabricating designs will hopefully mean increased opportunities to turn designs into silicon.

GF180’s first multi-project wafer (MPW) tapeout was in December 2022, and several people from the Zero to ASIC and Tiny Tapeout communities were able to submit designs. Here are some highlights:

Submit Tiny Tapeout Projects to an MPW

Using the Tiny User Project tool, people can quickly submit a Tiny Tapeout design to the MPW lottery. The low barrier to entry makes this a great tool to try variations on a design, test faster I/O speeds on an MPW tapeout, or simply compare tapeout processes using a different submission venue.

@Proppy developed the an easy-to-use tool as an extension to the Tiny Tapeout flow.

Proppy’s template repository uses GitHub actions to add a design to the Efabless Caravel User Project. The actions automatically perform the steps requried to harden the design, generate the necessary GDS files, and even generate a convenient GDS viewer. Additionally, the actions output useful reports on cell resource utilization, manufacturability errors, and the precheck results.

Tiny Tapeout 2 submitted for manufacture

I’m happy to announce that Tiny Tapeout 2 was successfully submitted for manufacture in December 2022! 164 designs were included on the tapeout.

Update! Tiny Tapeout 2 chips are back and working!

If you’re unfamiliar, Tiny Tapeout is an educational project that makes it easier and cheaper than ever to get your digital designs manufactured on a real chip! We had a first trial, Tiny Tapeout in September 2022 that was destined for MPW7.

Zero to ASIC course Ticket Grant

I am excited to introduce a grant for the Zero to ASIC course.

The grant will provide a Silicon-level ticket for selected participants. Two grants will be awarded per month.

Course goals

This course aims to revolutionize open-source silicon by training engineers, hobbyists and enthusiasts to make their own ASICs. During the course, you will design a circuit that will be submitted to the Google lottery MPW to be manufactured in silicon!

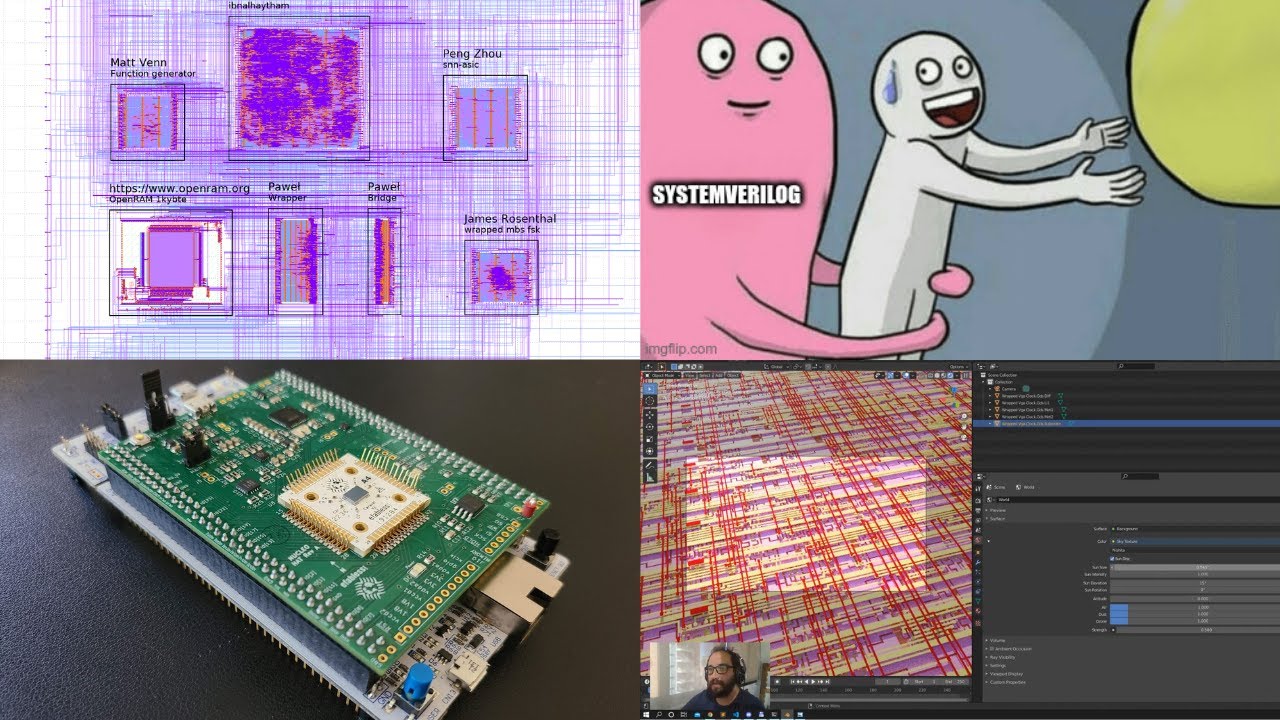

Monthly Update - September 2022

Welcome to the September 2022 monthly update!

Here are the main topics from last month:

- MPW7 submission,

- MPW2 updates,

- Job posting at E-Fabless,

- New videos,

- Is it the end for UVM? and

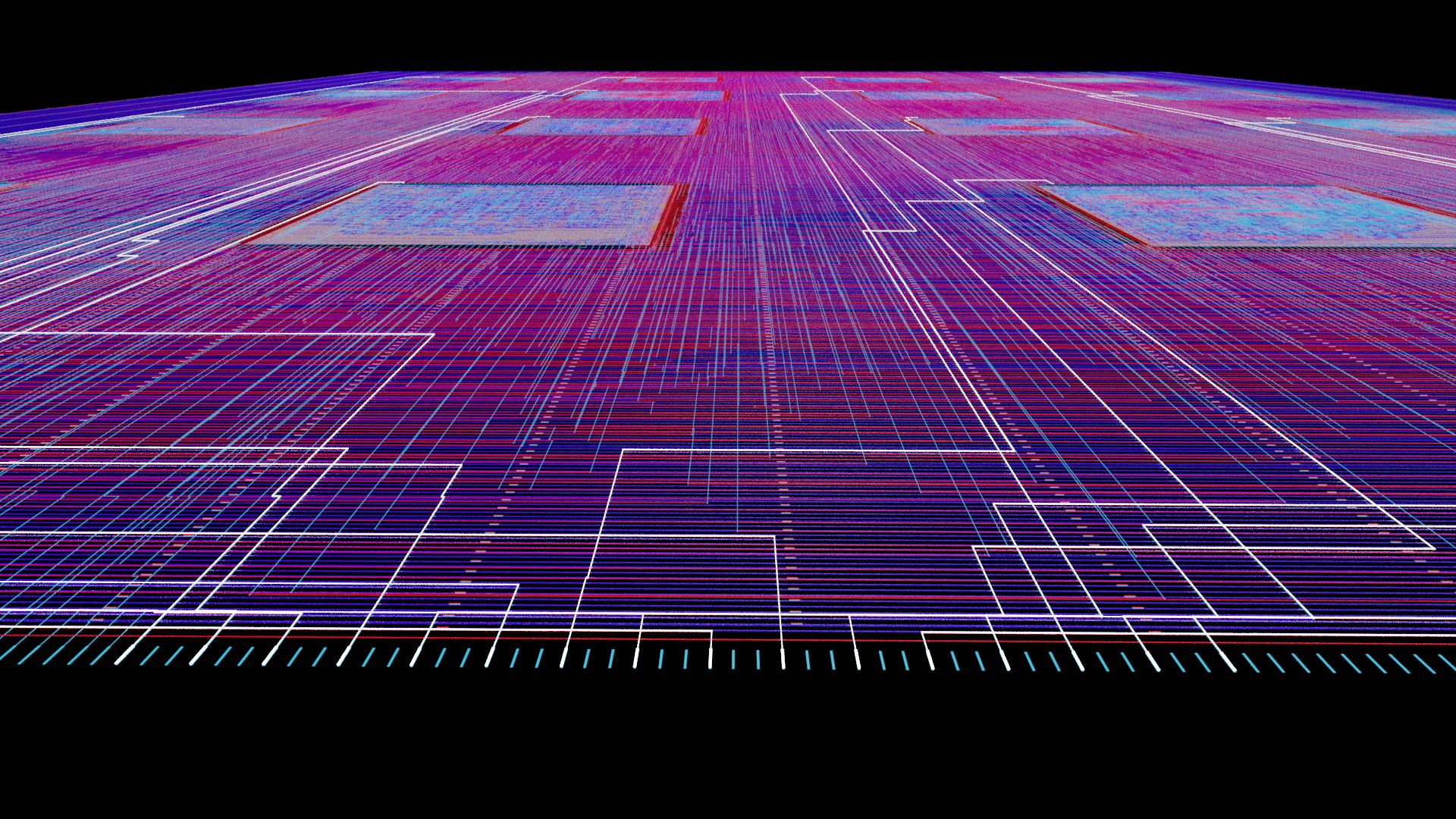

- Rendering GDS files with Blender or in your browser

MPW7

The deadline for MPW7 was the 14th of September and the Zero to ASIC course submitted another set of projects. Special shout out to Farhad, Peng and James who are all first time tape outs on the project. Well done everyone!