Below you will find pages that utilize the taxonomy term “Mpw”

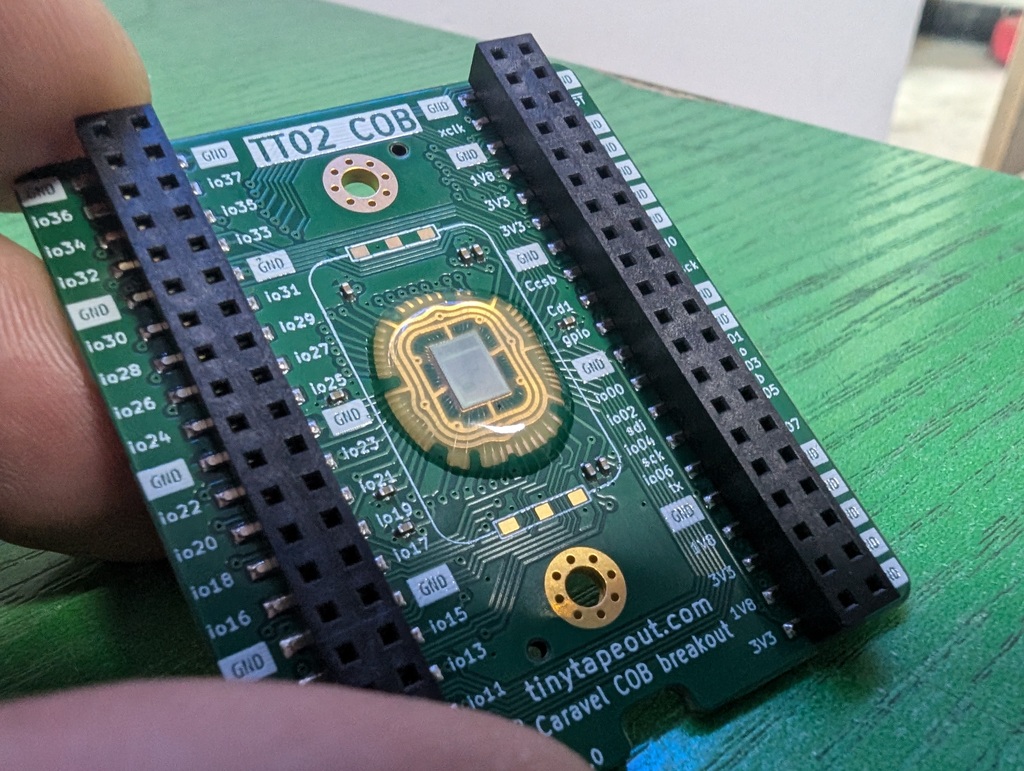

Chip On Board

Our first COB (chip on board) chips are working! This has been a dream of mine for a few years, and it’s finally a reality!

We’re used to seeing chips as little black boxes on a circuit board, but what’s inside?

The first part of the journey started with Tamas creating this cool circuit board.

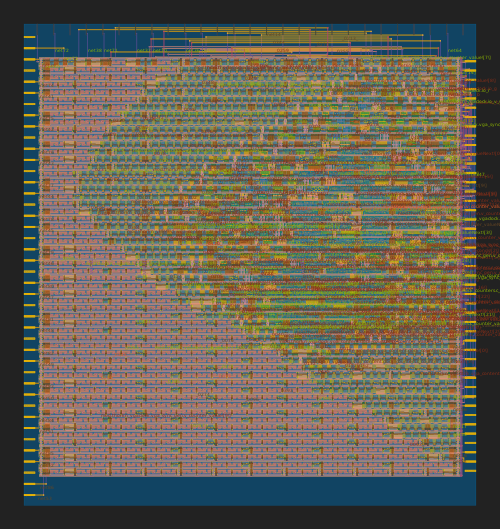

Tiny Tapeout 9

Tiny Tapeout 9 closed with 95% utilisation! It was our best ever run, with 369 designs submitted from 21 countries.

Among the digital projects we had an Atari 2600 (with games), a wide range of CPUs and even some SDR projects.

On the analog side we had PLLs, opamps, ADCs, DACs and time to digital converters.

For all the projects, check the chip’s page.

I printed the datasheet, and it’s hefty! Download it here.

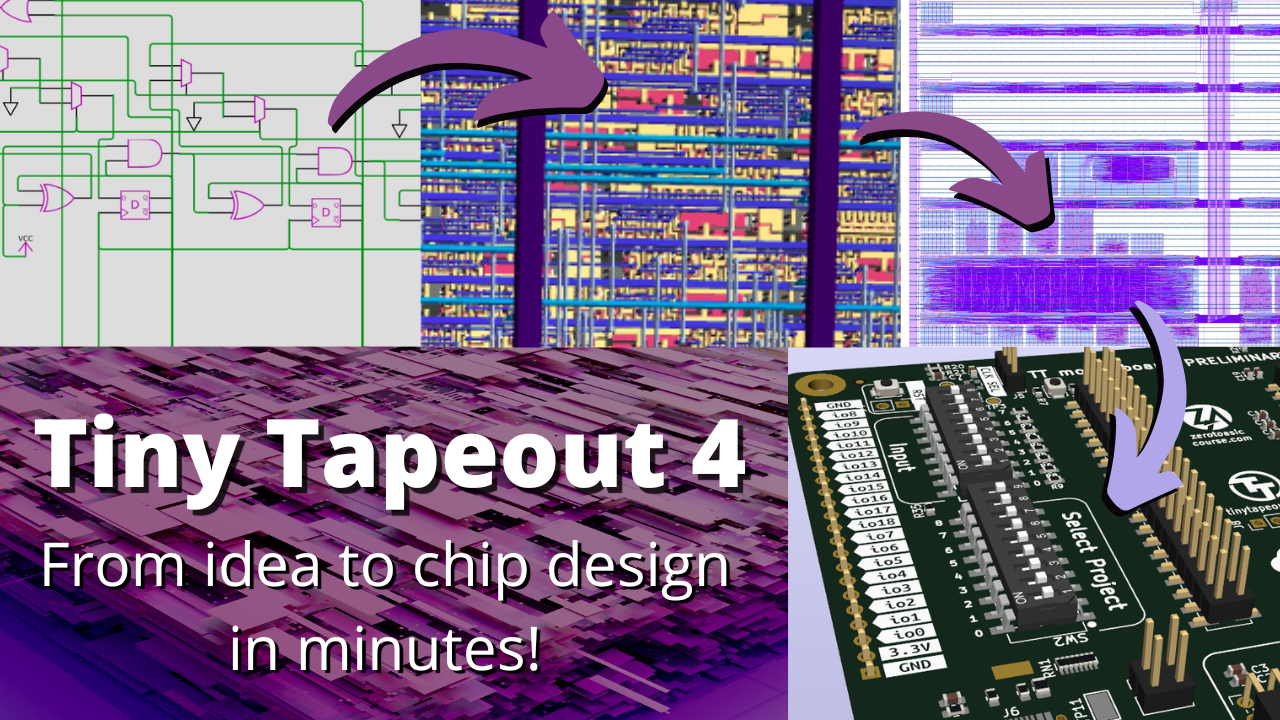

Tiny Tapeout 4

I’m very happy to have over 140 designs from 30 countries submitted to Tiny Tapeout 4!

Top level statistics:

- Total standard cells 82126

- Maximum cells used was 6813 for project 033

- Maximum utilisation was 87.18% for project 016

- Total wire length was 2607 mm

Thanks to everyone who submitted and all the contributors. Also a huge thanks to Efabless Corporation for sponsoring the project!

Tiny Tapeout 5 is already open and will close in early November 2023.

Cloud Tools for ASIC Development

ASIC development tools have often been inaccessible due to cost and complexity. Even as free, open-source tools have become available, the complexity of building and installing the tools has slowed their use by would-be designers.

A challenge in making ASIC development more accessible has been to provide free, easy-to-use development tools. Thankfully development of cloud-based tools using open-source software are making chip design easier than ever.

In June 2022, I had the chance to talk with @Proppy, a Tokyo-based Google engineer who’s enabling people to collaborative ASIC in the cloud with Jupyter and Colab notebooks.

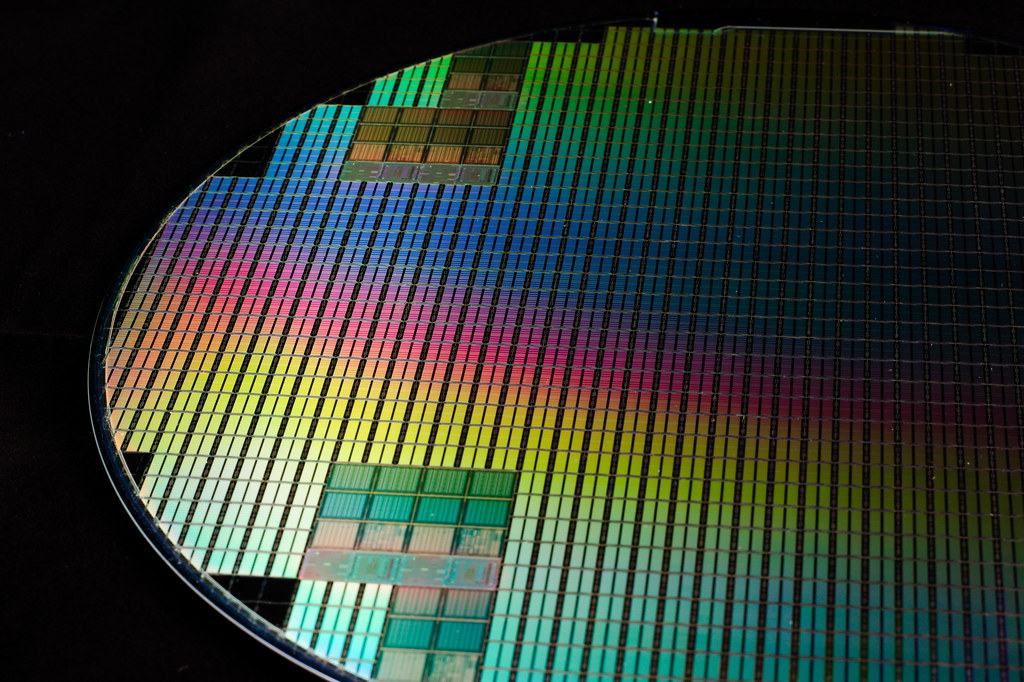

GlobalFoundries 180nm Fab

An exciting new opportunity for developing open-source silicon reached fruition at the end of 2022!

GlobalFoundries (GF) teamed up with Google to fund open-source projects using GF’s foundry and their open-source 180nm PDK GF180.

Open-source PDKs like GF180 and Skywater 130nm are essential for making silicon design more accessible. To now have GlobalFoundries involved with fabricating designs will hopefully mean increased opportunities to turn designs into silicon.

GF180’s first multi-project wafer (MPW) tapeout was in December 2022, and several people from the Zero to ASIC and Tiny Tapeout communities were able to submit designs. Here are some highlights:

Submit Tiny Tapeout Projects to an MPW

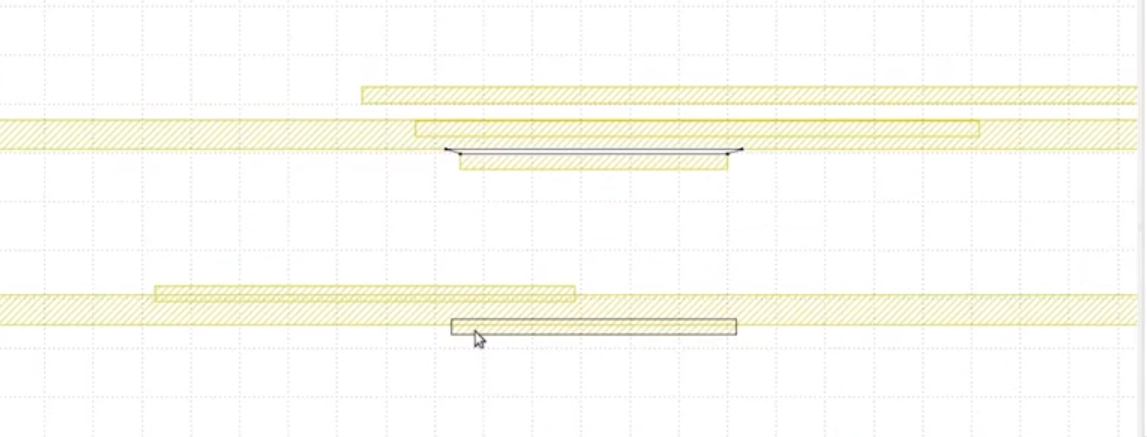

Using the Tiny User Project tool, people can quickly submit a Tiny Tapeout design to the MPW lottery. The low barrier to entry makes this a great tool to try variations on a design, test faster I/O speeds on an MPW tapeout, or simply compare tapeout processes using a different submission venue.

@Proppy developed the an easy-to-use tool as an extension to the Tiny Tapeout flow.

Proppy’s template repository uses GitHub actions to add a design to the Efabless Caravel User Project. The actions automatically perform the steps requried to harden the design, generate the necessary GDS files, and even generate a convenient GDS viewer. Additionally, the actions output useful reports on cell resource utilization, manufacturability errors, and the precheck results.

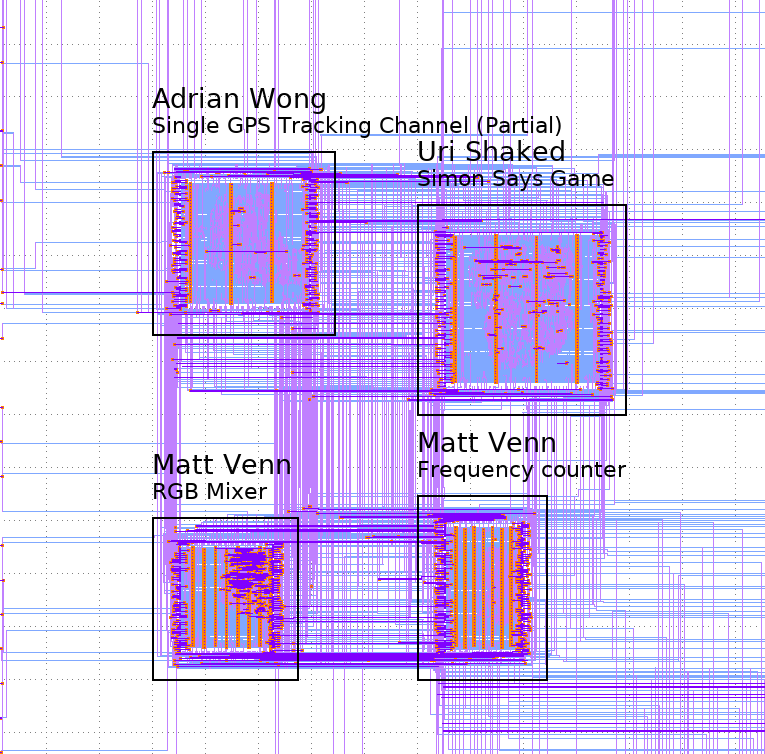

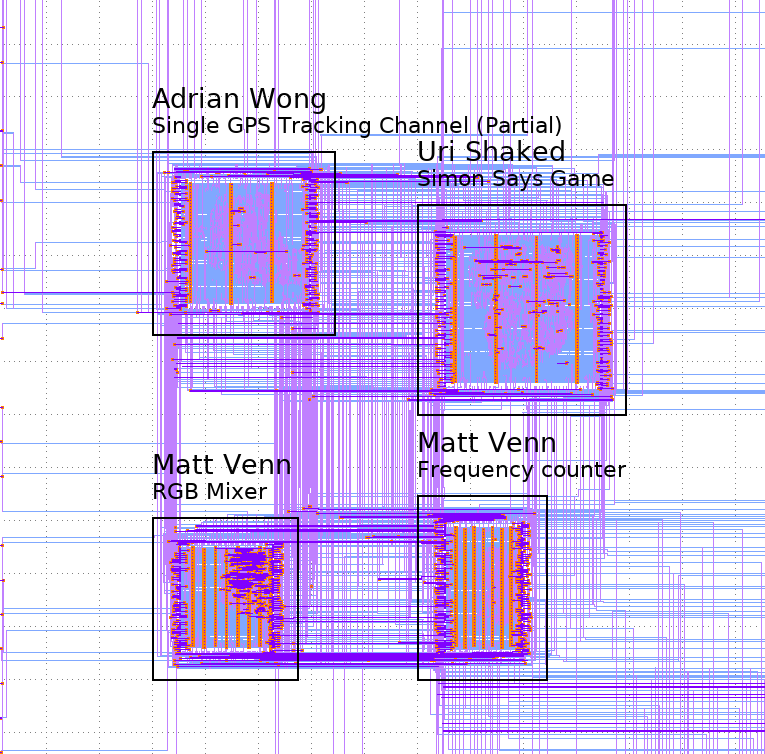

MPW8 submitted!

We submitted for MPW8! Special congratulations to Adrian Wong for the course submission!

We still managed to get 4 projects in the submission…not bad for a deadline of New Year’s Eve.

The projects include a partial implementation of an L1 GPS tracking channel by Adrian Wong, a Simon Says game implementated by Uri Shaked, and 2 demo submissions (frequency counter and RGB mixer) from me.

Here’s the github repo for the group submission and the Efabless project.

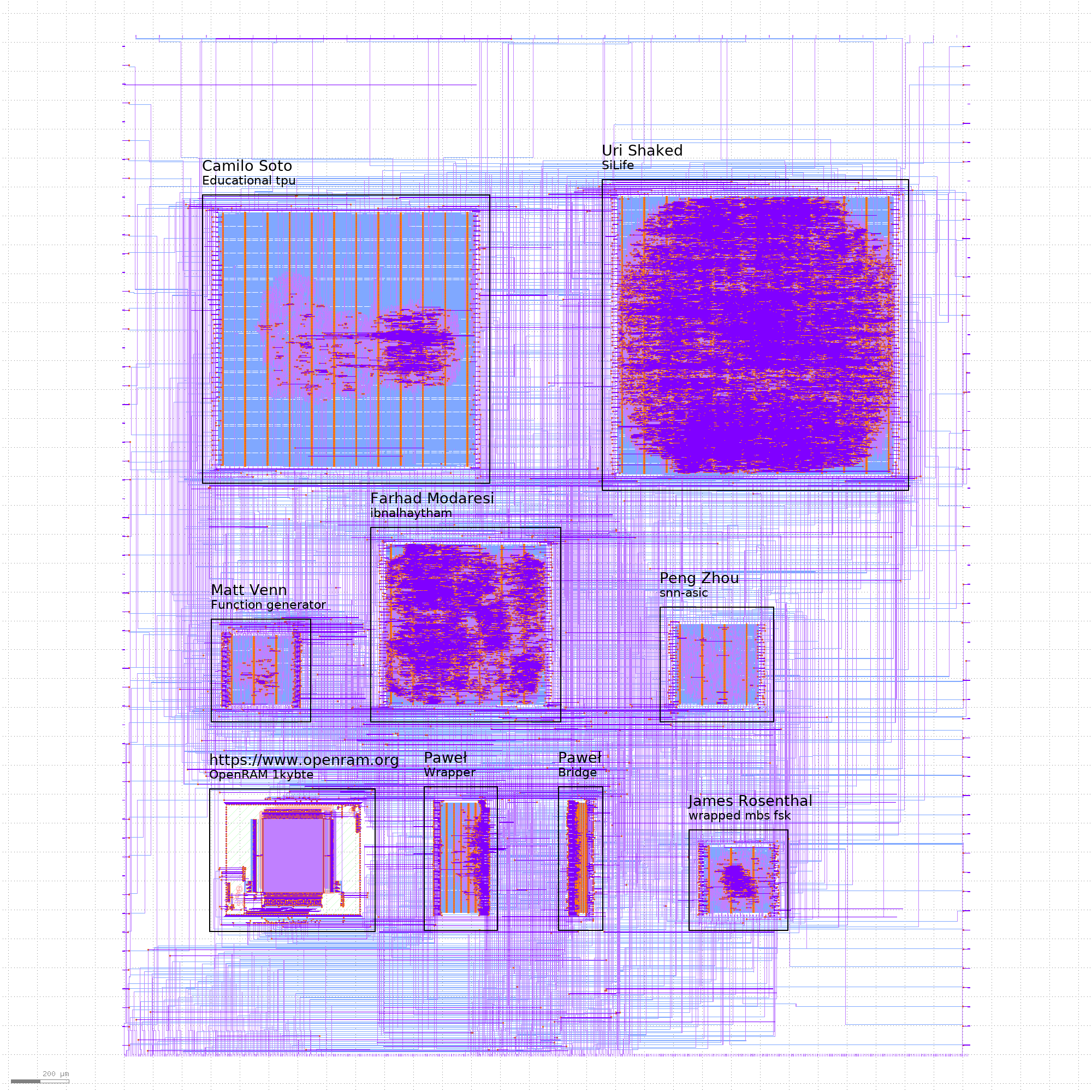

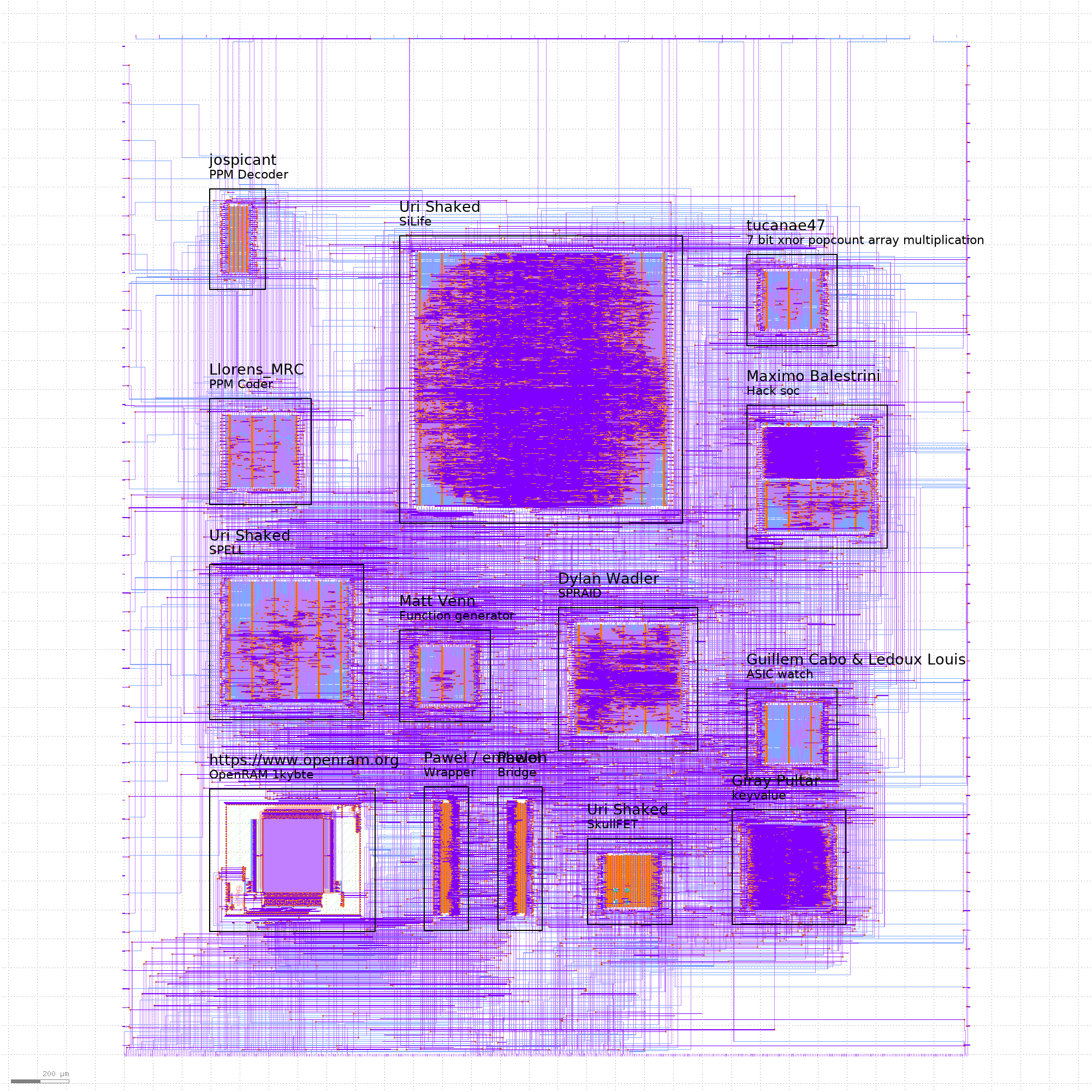

MPW7 submitted!

We submitted for MPW7! I am particularly excited about this submission because we were able to submit the Zero to ASIC course designs as well as the first Tiny Tapeout design.

MPW7 has by far had the most submissions of the MPW shuttles so far with 72 submitted projects as of 13 September.

Congratulations to everyone on the course submission! We had 9 projects from the course, with 1 demo arbitrary function generator from me, a 32-bit RISC-V based processor by Farhad, an in silicon version of Conway’s Game of Life from Uri and a Spiking Neural Network (SNN) accelerator by Peng Zhou. We also implemented 1kByte of RAM with open-source OpenRAM.

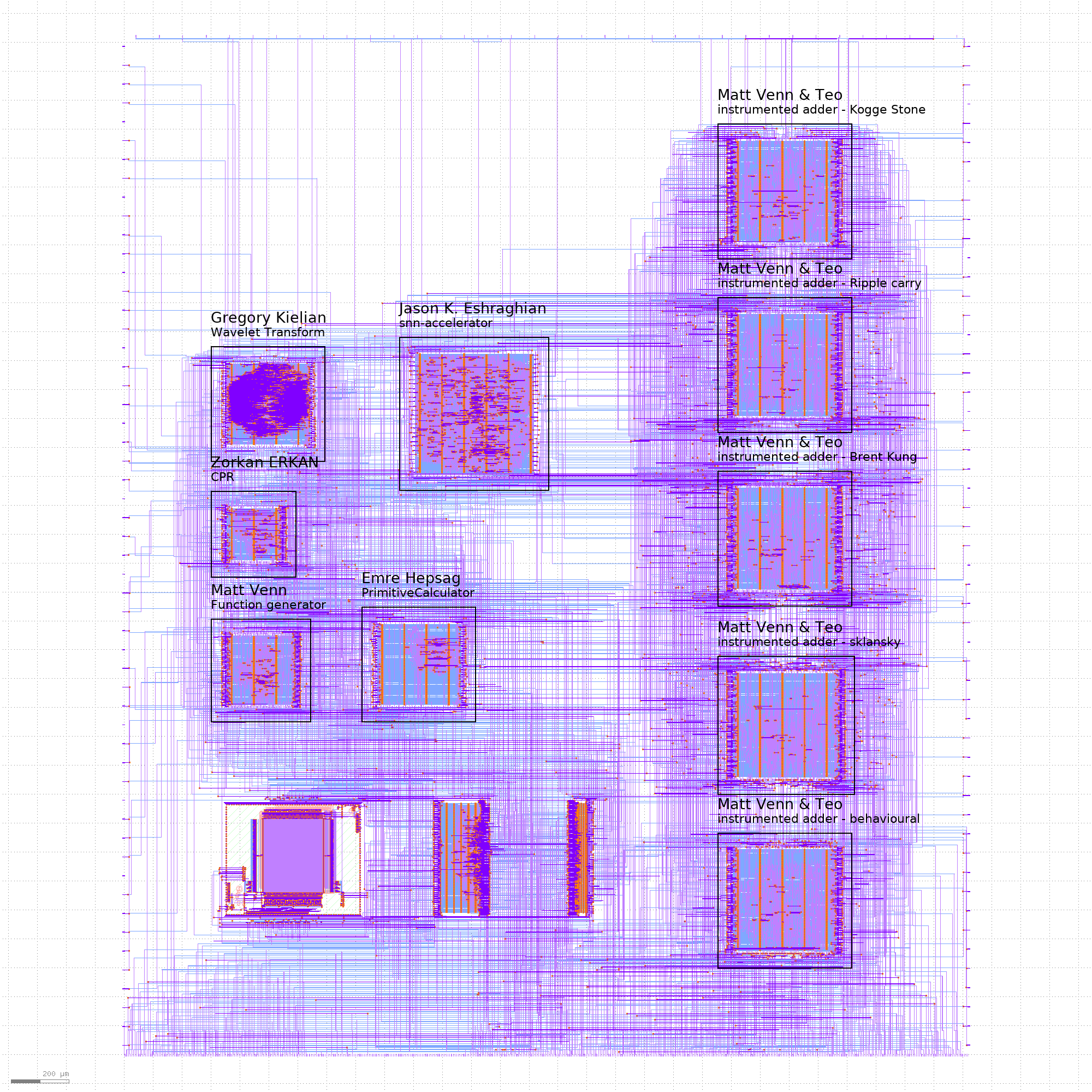

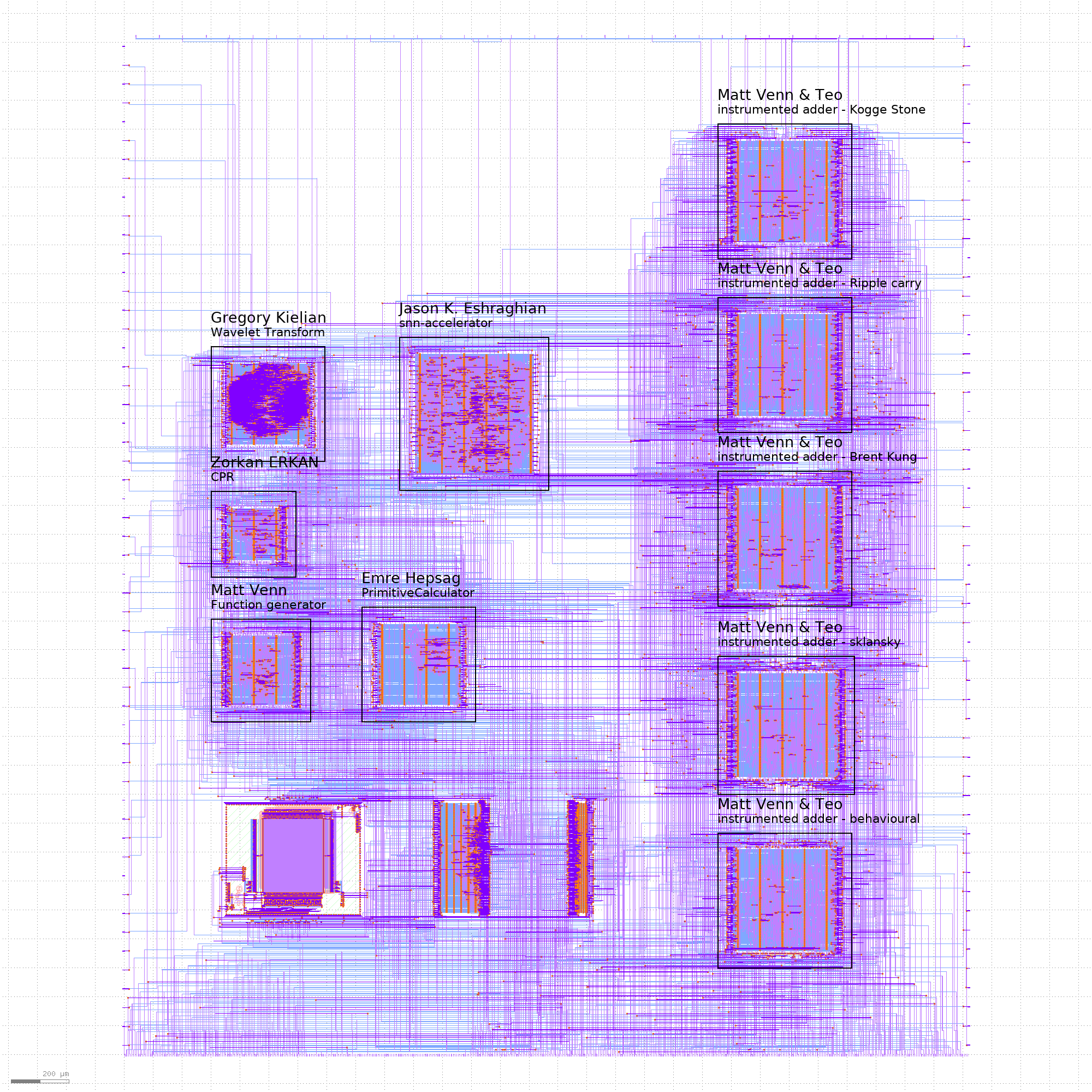

MPW6 submitted!

We submitted for MPW6!

We had 4 submissions from the course, the shared SRAM infrastructure, and I did some work on instrumenting Teo’s hardware adders.

Congratulations to:

- Zorkan ERKAN

- Emre Hepsag

- Gregory Kielian

- Jason K. Eshraghian

for getting your first ASIC designs on the submission!

We also had some people from the course make personal applications for a whole chip:

- Shumpei Kawasaki - MARMOT SOC

- Maximo - Hardware implementation of the Hack Computer from the Nand to Tetris courses,

- Proppy - HSV Mixer

Here’s the github repo for the group submission and the Efabless project.

MPW5 submitted!

We submitted for MPW5!

We had 8 submissions from the course, the shared SRAM infrastructure, and I updated my demo designs.

We also had some people from the course make personal applications for a whole chip:

- Steve & Zhenle - PSRAM (HyperRAM) interface with an ACORN PRNG,

- Q3K - simple, microcontroller-style SoC based around a Lanai core,

- Maximo - Hardware implementation of the Hack Computer from the Nand to Tetris courses,

- Zbigniew - A rendering circuit for three blobs and a playable tetris clone.

And thanks to Paweł for updating the shared SRAM blocks.

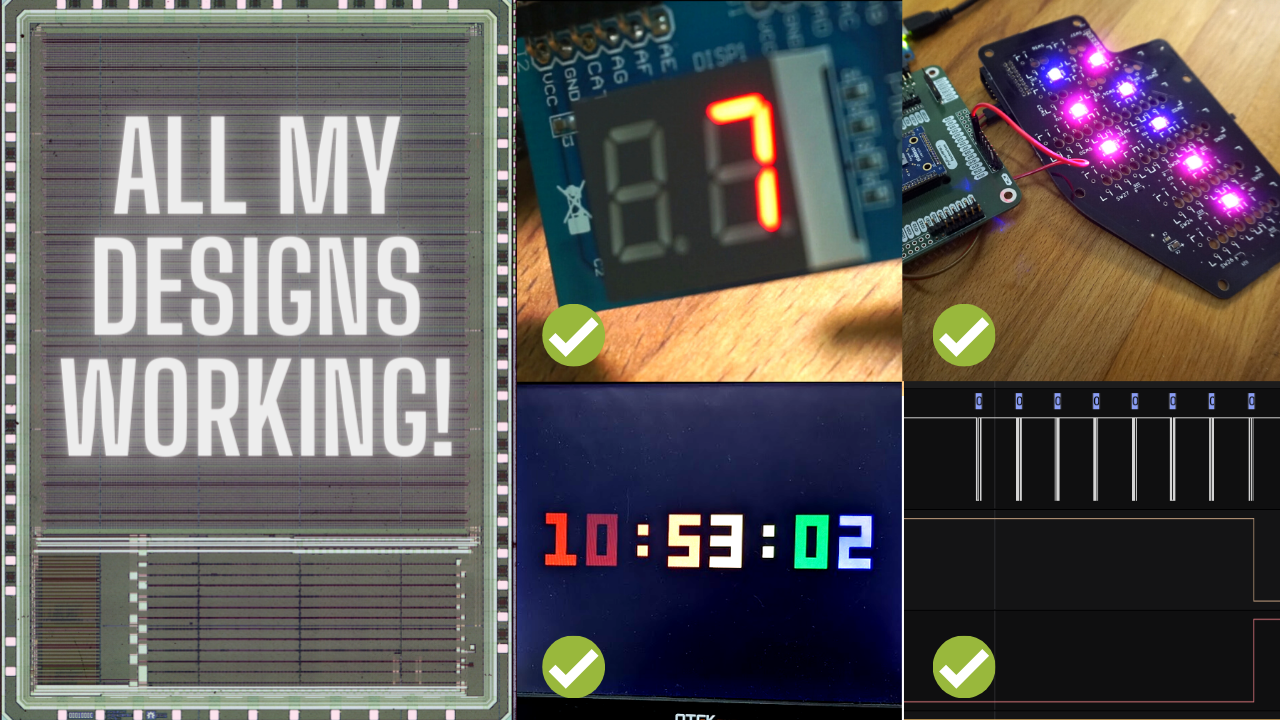

MPW1 is Alive

Yes! All the designs I submitted to MPW1 are working:

- ✅ 7 segment display

- ✅ TPM2137 CTF

- ✅ WS2812 led driver

- ✅ VGA clock

- ✅ Multiplexor

I put together a video to demonstrate them all:

The 4 other designs that were part of this submission were made by friends who I’ve now sent samples to. It’s looking likely that everyone’s designs will work.

MPW1 Bringup

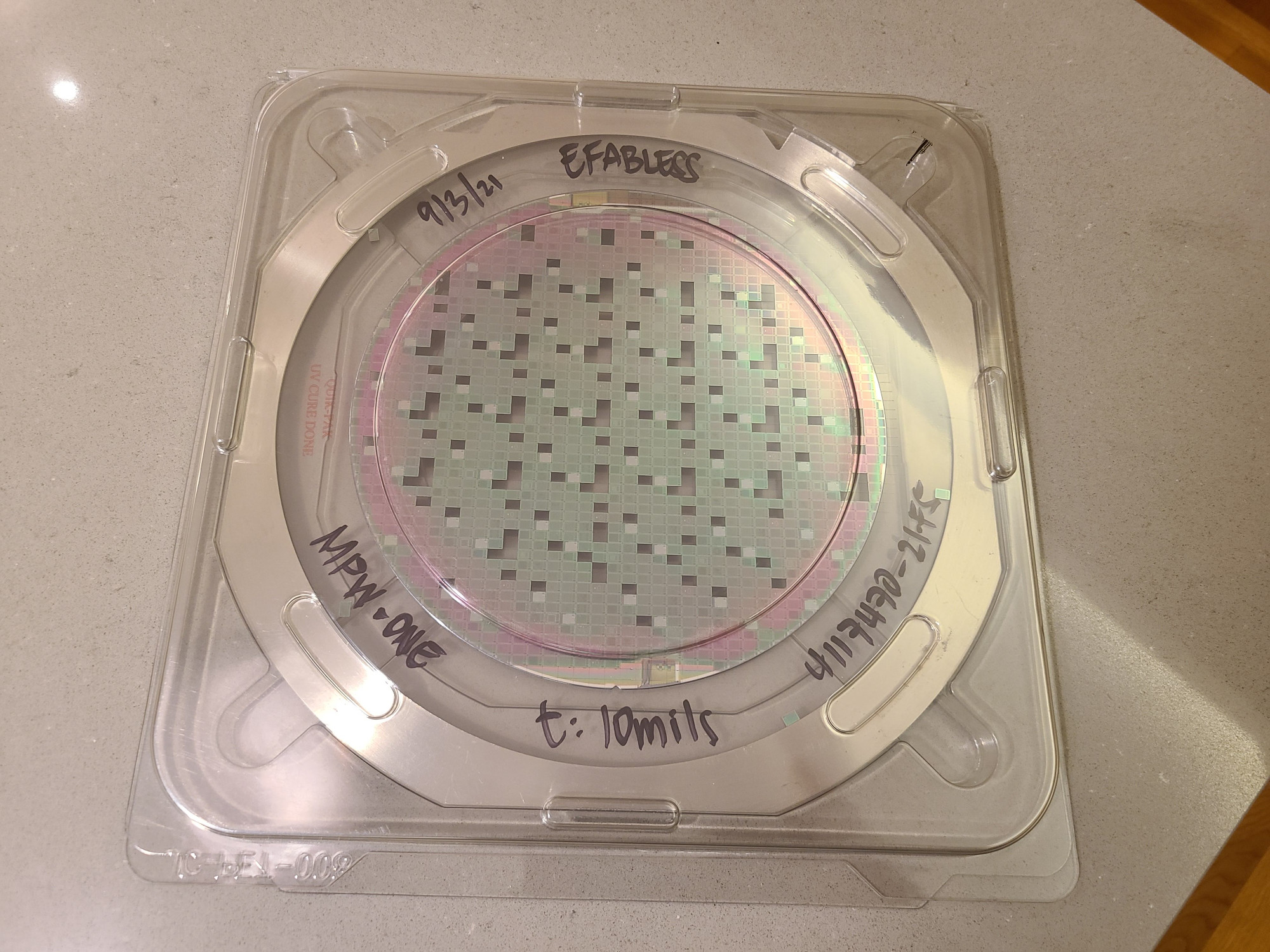

I submitted my first ASIC designs to the free Google shuttle in December of 2020.

In October 2021, we heard there were serious clock related problems with the management area of the chip due to issues with the toolchain. It seemed unlikely that anyone would be able to get anything beyond a single blinking LED from MPW1. The hold violations in the management system meant that the PicoRV32 cpu couldn’t run and setup the GPIOs. So even if our designs work, we can’t get access to them.

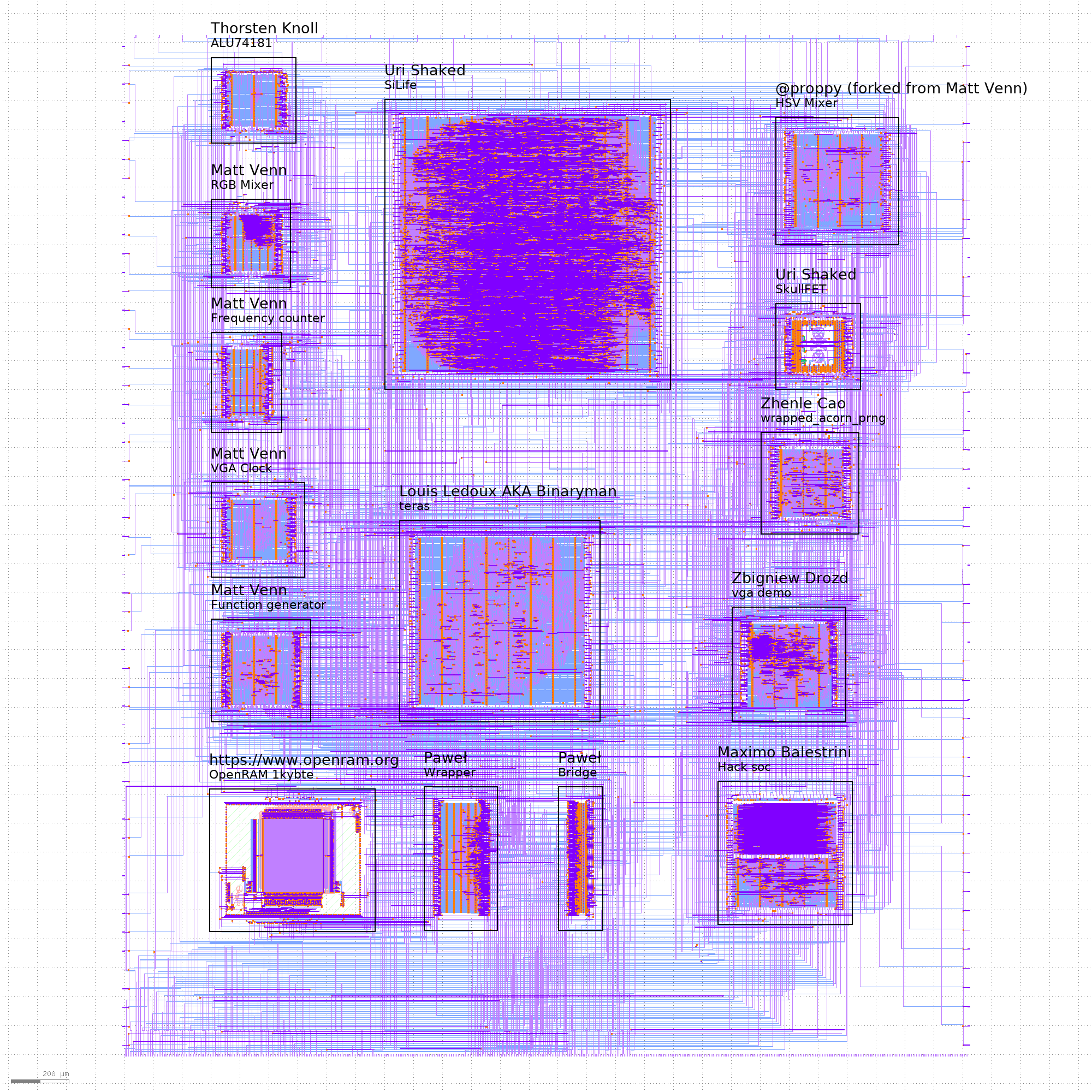

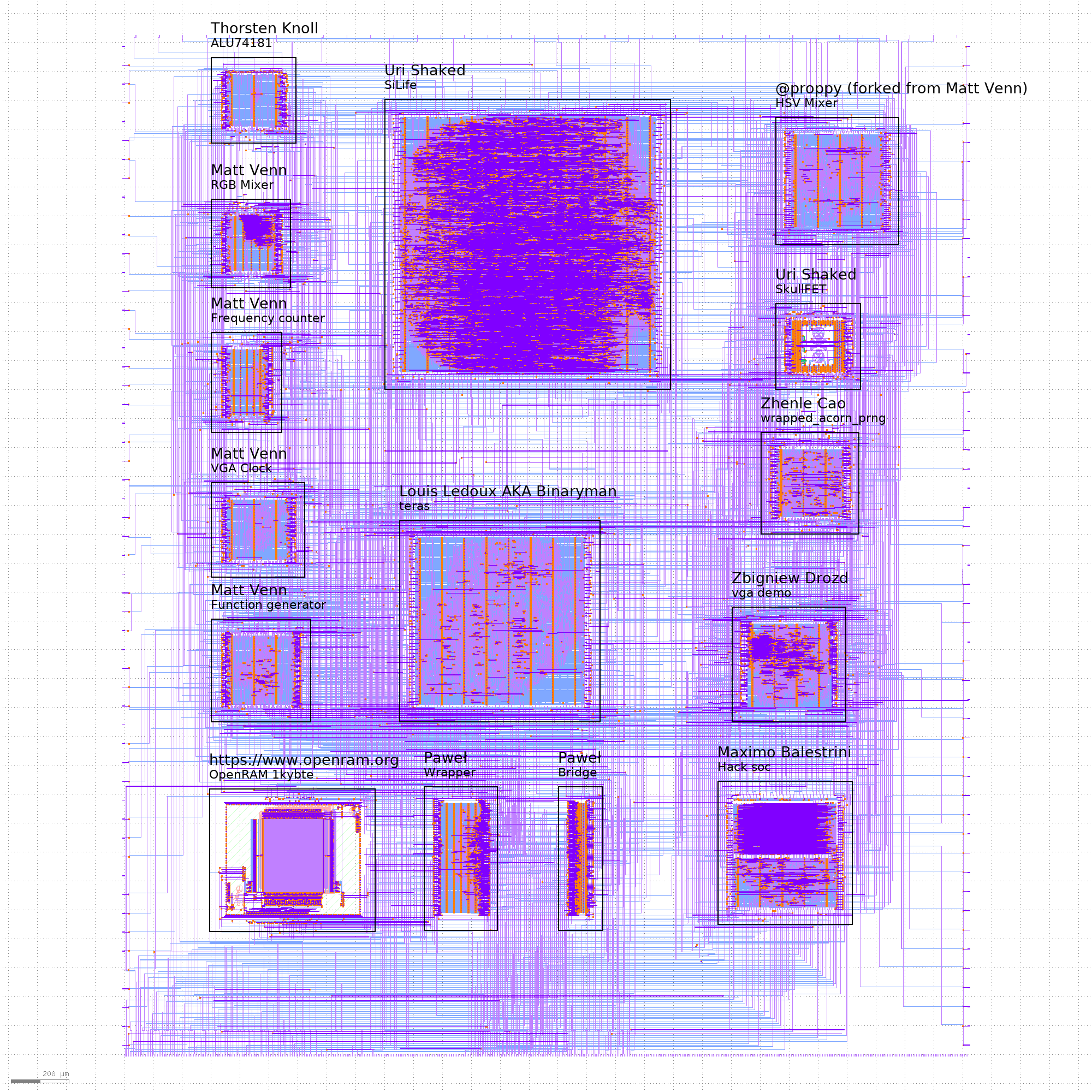

MPW4 submitted!

We submitted for MPW4! I was pretty pleased we managed to get so much in with such little time and for a tapeout date of New Year’s Eve.

We had 9 submissions from the course, with 1 demo project from me and a new version of Maximo’s hacksoc. Uri submitted 3 designs including some custom standard cells in the shape of skulls!

We also implemented the shared SRAM, which means that the group projects have access to a local fast memory (like a blockram on an FPGA).

MPW3 submitted!

We submitted for MPW3! The tapeout date was delayed by a couple of weeks due to issues with the toolchain.

Update!

We received silicon in June 2023 (18 months later!) and I was able to get both my designs partially working.

MPW3

We had 7 new submissions from the course, 4 repeats from MPW1 and 2 with fixed clock trees, a new wishbone demo from me and the OpenRAM block.

MPW1 silicon has serious problems

MPW1 seems an age ago, we submitted in December 2020, but it needed some last minute DRC fixes in February.

Silicon was received a few weeks ago, and unfortunately we have some serious issues that will prevent most designs from working. This appears to be due to a bad clock tree in the management section of the chip. Additionally, OpenSTA, the tool meant to verify the clock tree was also misconfigured.

The initial announcement is here.

MPW2 Submitted

We did it! 14 people from the course got their designs into the group submission, and the project was accepted for fabrication. Silicon here we come!

You can get all the details on all the projects submitted to MPW2 here - you’ll need to select the MPW2 filter.

And see how I put the application together here, with the repo here.

Project listing

RGB Mixer

- Author: Matt Venn

- Github: https://github.com/mattvenn/wrapped_rgb_mixer/tree/caravel-mpw-two-c

- Description: reads 3 encoders and generates PWM signals to drive an RGB LED

Frequency counter

- Author: Matt Venn

- Github: https://github.com/mattvenn/wrapped_frequency_counter/tree/caravel-mpw-two-c

- Description: Counts pulses on input and displays frequency on 2 seven segment displays

A5/1 Wishbone

- Author: Jamie Iles

- Github: https://github.com/jamieiles/a5-1-wb-macro

- Description: A5/1 cryto block connected via wishbone to PicoRV32

Fibonacci

- Author: Konrad Rzeszutek Wilk

- Github: https://github.com/konradwilk/fibonacci

- Description: Fibonacci emitter connected to [37:8] and controlled via wishbone

Quad PWM FET Drivers

- Author: Chris DePalm

- Github: https://github.com/ChrisDePalm/wrapped_quad_pwm_fet_drivers.git

- Description: 4 PWM FET Drivers for Power Applications

memLCDdriver

- Author: Matt Beach

- Github: https://github.com/matt-beach/wrapped_memLCDdriver.git

- Description: SPI to 64-color memory LCD interface

QARMA-64 Accelerator

- Author: Viktor H. Brange

- Github: https://github.com/vbrange/verilog_qarma

- Description: Implementation of QARMA 64

ChaCha20 Accelerator

- Author: Richard Petri

- Github: https://github.com/rpls/wrapped_chacha_wb_accel

- Description: A minimal Wishbone connected ChaCha20 accelerator

Framebufferless Video Core

- Author: Tom Gwozdz

- Github: https://github.com/tomgwozdz/fbless-graphics-core

- Description: A framebufferless VGA video generator, under CPU control

Pong

- Author: Erik van Zijst

- Github: https://github.com/erikvanzijst/wrapped_pong.git

- Description: A hardware implementation of Pong

Hack soc

- Author: Maximo Balestrini

- Github: https://github.com/mbalestrini/wrapped_hack_soc

- Description: Hardware implementation of the Hack Computer from the Nand to Tetris courses

gfxdemo

- Author: Konrad Beckmann

- Github: https://github.com/kbeckmann/wrapped_gfxdemo

- Description: gfxdemo

Wishbone HyperRAM

- Author: Pawel Sitarz

- Github: https://github.com/embelon/wrapped_wb_hyperram

- Description: Simple HyperRAM driver accesible on Wishbone bus

Newmot SoC

- Author: Charles-Henri Mousset

- Github: https://github.com/chmousset/caravel_multi_newmot

- Description: Simple SoC dmonstrating a Stepper Motor step/dir generator, and litex wishbone / uart / pwm

hoggephase

- Author: David Hulton

- Github: https://github.com/h1kari/wrapped_hoggephase_project

- Description: Hogge Phase EMFI/BBI Glitch Detector

bfloat16_fma

- Author: Author

- Github: https://github.com/etalian/mensa

- Description: dual bfloat16 fused multiply-add

Multi project tools

This time around submission was a lot easier and nerve-wracking than MPW1.

MPW2 announced by Efabless

Efabless have announced MPW2! The closing date is the 18th of June.

The biggest changes are:

- OpenLANE ASIC flow updated to rc0.15

- Caravel has become caravel_user_project at the mpw-two-c tag:

- smaller repo size includes a ‘Caravel Lite’ submodule

- new IRQ ports

- logic analyser registers renamed

- An alternative analogue specific ‘Caravan’ harness

- The submission process has been streamlined to make it faster and easier to submit

You can browse the current applications here: https://platform.efabless.com/projects/shuttle_name/MPW-2

Last minute DRC fixes

The story of the first Open Source ASIC shuttle continues!

A few of the applicants to the first shuttle were recently contacted by efabless - they had discovered some DRC issues that couldn’t be waived by the foundry.

In my recent interview with Tim Edwards, he mentioned that Google are paying for a license of Calibre - another swiss army ASIC tool like Magic. This is to help make sure that the OpenLANE DRC hasn’t missed anything.

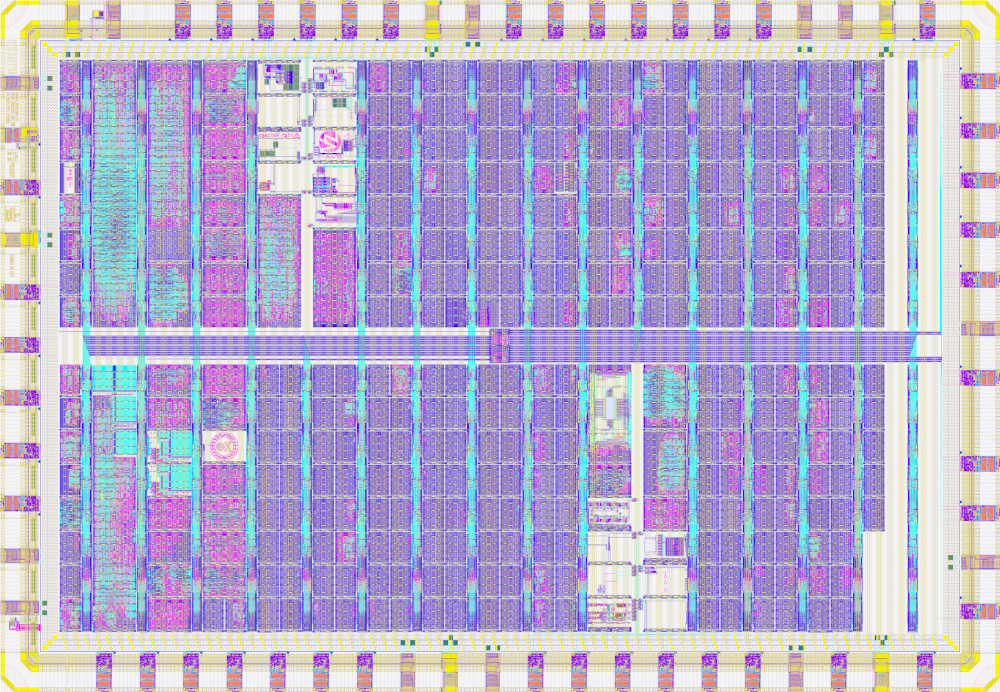

My first ASIC - MPW1 submitted

Wow! What a journey. I’m very happy to announce our submission is in and accepted. Now we have a long wait to see if it works! (it does! Jump to the end for an update).

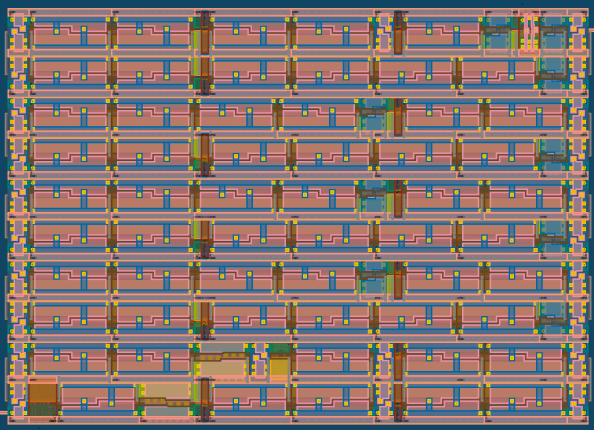

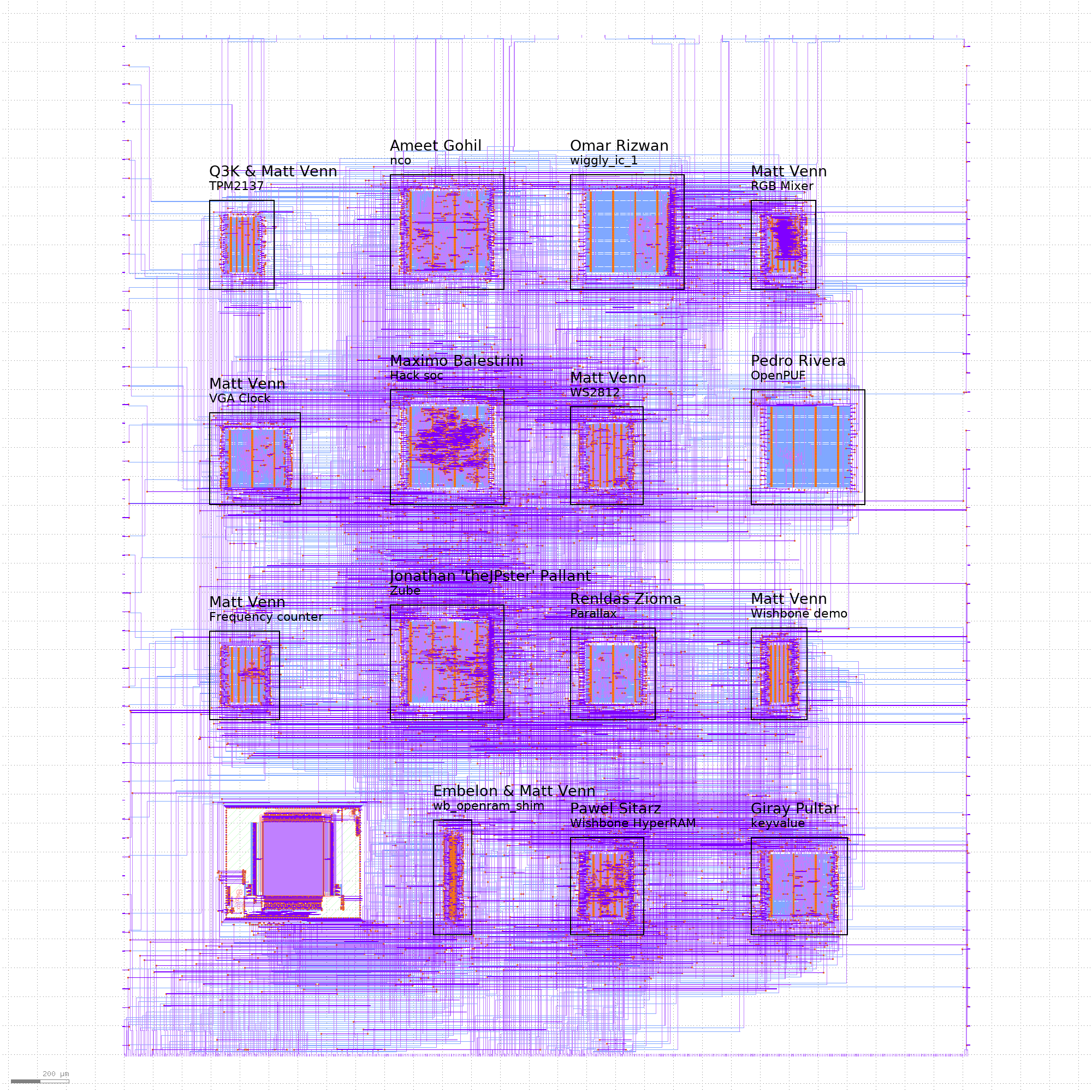

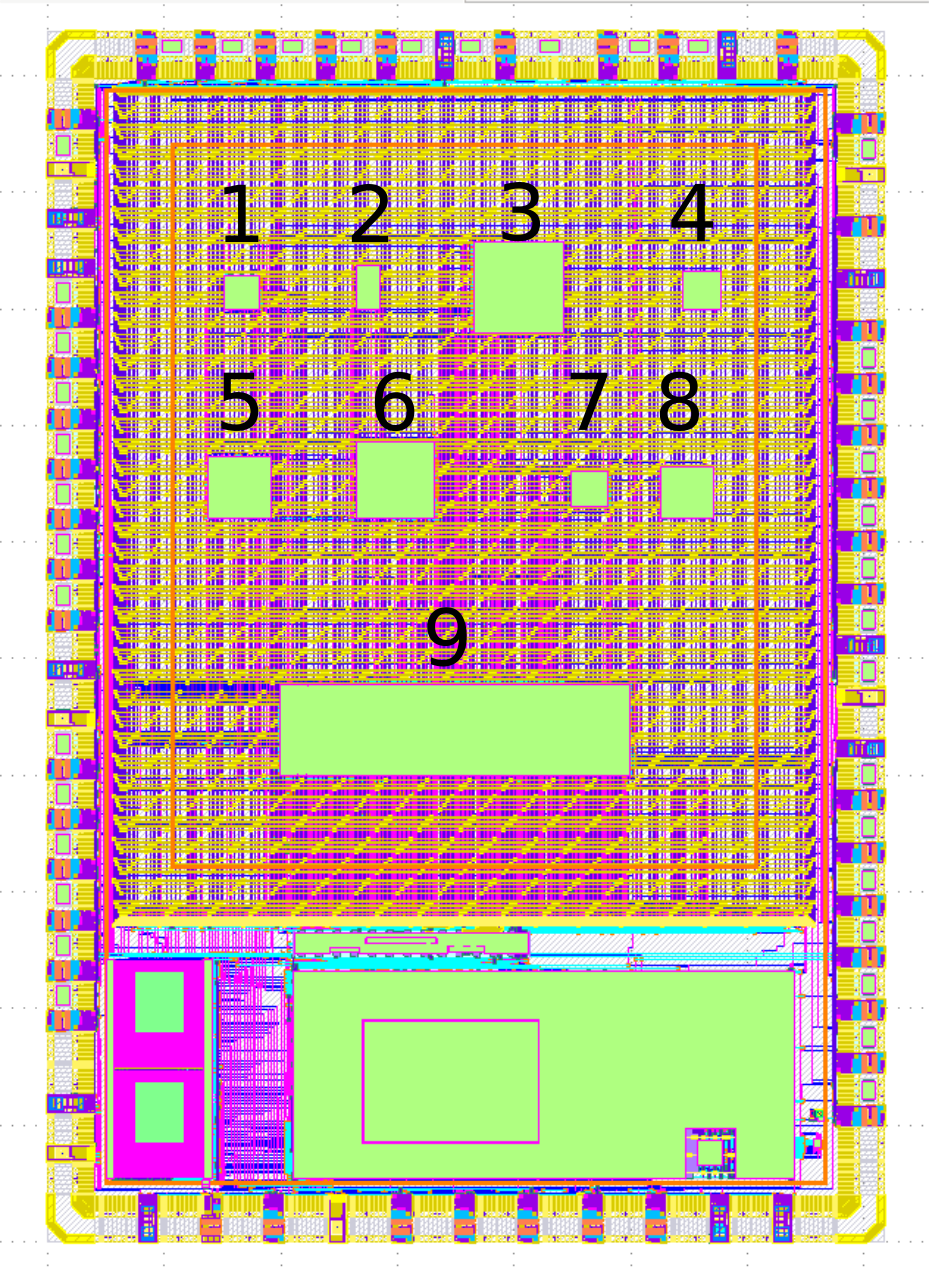

Here’s a picture of the final design. The outer edge and the block at the bottom are all part of Caravel, the standard chip format that everyone on the shuttle has to use. It includes a RISCV processor, RAM, UART, a wishbone bus and more.

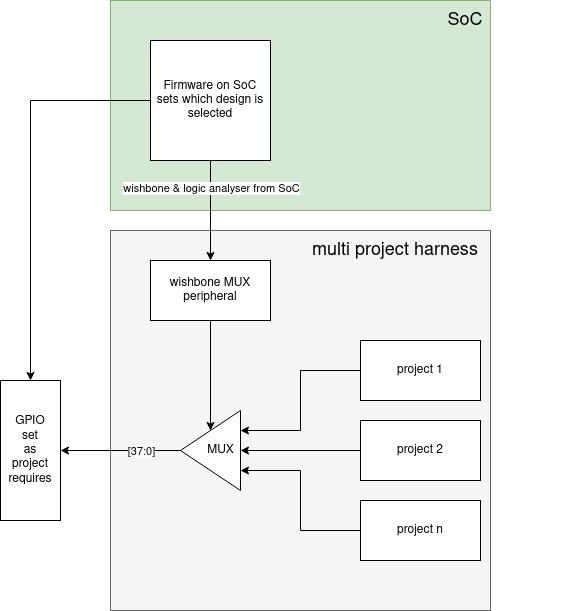

Multi Project Harness

The Google/Skywater Shuttle has about 10 square mm of space for your project. This sounds tiny but is actually HUGE for many beginner projects. Read this post to find out what you could fit in the user space.

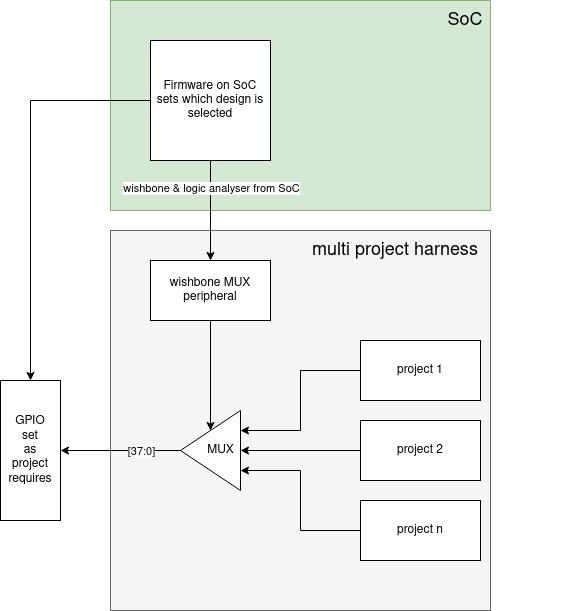

For the Zero to ASIC course, I want to aggregate all your designs together into that area, so we need to do some extra bits:

- Multiplex all the inputs and outputs of your project to the GPIO pins of the Caravel harness.

- Connect important signals like clocks and make sure the tools know they are special

- there will need to be a bit of firmware on the SoC that sets up the GPIOs for each design and sets it active.